**REVIEW ARTICLE**

# Survey and Future Directions on Fault Tolerance Mechanisms in Reconfigurable Computing

#### A.Surendar

Saveetha Institute of Medical and Technical Sciences, Saveetha University, Chennai, India

#### **KEYWORDS**:

Fault Tolerance, Reconfigurable Computing, Field-Programmable Gate Arrays (FPGAs), Error Detection and Correction

ARTICLE HISTORY:

Submitted:

21.01.2024

Revised:

17.02.2024

Accepted:

16.03.2024

DOI: https://doi.org/10.31838/rcc/01.01.06

#### Abstract

This paper provides an extensive review of fault tolerance mechanisms in reconfigurable computing, particularly focusing on Field-Programmable Gate Arrays (FPGAs). Reconfigurable computing systems offer significant flexibility and performance advantages but are vulnerable to various faults that can compromise system reliability. The review starts with an introduction to the importance of fault tolerance in reconfigurable computing, followed by a detailed examination of existing mechanisms, including redundancy techniques, error detection and correction methods, and dynamic reconfiguration strategies. The discussion highlights the challenges involved in implementing fault tolerance, such as the tradeoffs between performance and reliability and the increased complexity of faulttolerant designs. Through case studies, the effectiveness and practical application of different fault tolerance strategies are illustrated. The paper also explores emerging trends and innovations, such as the integration of machine learning techniques and advancements in self-healing systems. The conclusion emphasizes future research directions, advocating for the development of more efficient, scalable, and automated fault tolerance solutions to improve the robustness of reconfigurable computing systems.

Author's e-mail: surendararavindhan@ieee.org

**How to cite this article:** Surendar A, Survey and Future Directions on Fault Tolerance Mechanisms in Reconfigurable Computing. SCCTS Transactions on Reconfigurable Computing, Vol. 1, No. 1, 2024 (pp. 26-30).

## INTRODUCTION

Fault tolerance is a critical aspect of reconfigurable computing, particularly in systems that utilize Field-Programmable Gate Arrays (FPGAs). These systems are widely used across various applications due to their flexibility and ability to be reprogrammed for specific tasks [1]. Unlike traditional fixed architectures such as CPUs and ASICs, FPGAs offer dynamic customization capabilities that optimize performance, energy efficiency, and functionality. This makes them suitable for tasks requiring high processing speeds, minimal latency, and efficient resource management.

The concept of fault tolerance emerges from the understanding that hardware components, including FPGAs, are prone to failures due to environmental factors, wear and tear, and inherent manufacturing defects. Fault tolerance strategies are implemented to mitigate these risks by ensuring continuous system operation despite hardware faults. This is particularly crucial in industries where system downtime can lead to significant financial losses or safety hazards.

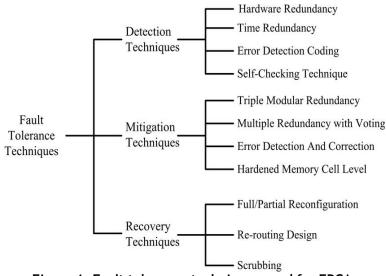

computing, In reconfigurable fault tolerance mechanisms encompass several strategies. These include redundancy, error detection and correction, fault isolation, and recovery (Figure 1) [2]. Redundancy involves duplicating critical components or computations within the system to ensure that if one fails, another can seamlessly take over. Error detection and correction techniques add additional bits to data streams or utilize algorithms to reconstruct corrupted data, thereby preserving data integrity. Fault isolation techniques pinpoint the location and nature of faults, facilitating swift recovery actions such as reconfiguring FPGAs to bypass faulty circuits or rerouting data.

Figure 1. Fault tolerance techniques used for FPGAs

Fault tolerance is essential not only in traditional computing environments but also in emerging fields like Internet of Things (IoT) and edge computing. In IoT applications, where devices are interconnected and operate in diverse environments, fault tolerance ensures reliable performance despite potential

hardware failures or network disruptions [3]. Similarly, in edge computing, which demands real-time processing near data sources, fault tolerance mechanisms enable FPGAs to maintain high availability and responsiveness.

Figure 2. Applications of IoT

Looking forward, advancements in fault tolerance for reconfigurable computing may incorporate technologies such as artificial intelligence (AI) and machine learning (ML) to enhance predictive capabilities. These innovations aim to preemptively address potential failures before they occur, thereby further enhancing system reliability and efficiency [4]. Additionally, ongoing developments in hardware design and faulttolerant architectures will continue to bolster system robustness and support increasingly complex applications.

# Current Fault Tolerance Mechanisms in Reconfigurable Computing

Fault tolerance mechanisms are critical in reconfigurable computing, especially in systems using Field-Programmable Gate Arrays (FPGAs), to ensure reliability despite hardware faults and errors. As FPGAs find application in critical fields demanding high reliability, robust fault tolerance strategies are indispensable. Current mechanisms can be broadly divided into redundancy techniques, error detection and correction methods, and dynamic reconfiguration strategies.

Redundancy is a cornerstone of fault tolerance. It involves duplicating essential components to maintain system functionality if one component fails. This can be achieved through various forms of redundancy: informational. spatial, temporal, and Spatial redundancy, like Triple Modular Redundancy (TMR), involves triplicating critical components and using majority voting to determine the correct output [5]. This ensures correct operation even if one component fails, as the remaining two can override the faulty one. Temporal redundancy involves repeating the same operation multiple times and comparing the results to identify and correct errors.

Error detection and correction (EDAC) techniques are also pivotal in reconfigurable computing. These methods add extra information to the data being processed to detect and rectify errors. Examples include parity bits, checksums, and more sophisticated methods like Hamming codes and Cyclic Redundancy Checks (CRC) [6]. Upon detecting an error, these methods can correct it immediately or prompt the system to take corrective actions, such as re-executing the operation or activating redundant components.

Dynamic reconfiguration is a unique strength of reconfigurable computing that bolsters fault tolerance. FPGAs can be reprogrammed in real-time to bypass faulty components and reallocate resources, thus maintaining system functionality. This allows for realtime adaptation to faults, minimizing downtime. Partial reconfiguration, where only a portion of the FPGA is reconfigured while the rest of the system remains operational, is especially valuable in critical applications requiring high availability.

Advanced fault tolerance mechanisms also exploit the parallelism and flexibility of FPGAs. For example, runtime hardware reconfiguration enables the creation of self-healing systems that detect and isolate faulty FPGA regions and reconfigure the hardware to use nonfaulty areas. Integrating machine learning algorithms into fault tolerance strategies is becoming more common, allowing for the prediction and preemptive addressing of potential faults based on historical data and real-time monitoring.

#### **Challenges in Implementing Fault Tolerance for Reconfigurable Architectures**

Implementing fault tolerance in reconfigurable architectures, particularly those utilizing Field-Programmable Gate Arrays (FPGAs), presents a host of formidable challenges. These difficulties stem from the intrinsic complexity and dynamic characteristics of reconfigurable computing, alongside the rigorous demands of their application environments [7]. Tackling these issues is essential for developing reliable and robust reconfigurable systems.

A primary challenge is the intricate nature of designing fault-tolerant systems. FPGAs offer extensive flexibility, capable of being reprogrammed to execute a

variety of tasks, but this flexibility demands a deep understanding of both hardware and software for faulttolerant design. Engineers must anticipate various fault scenarios, including transient faults caused by radiation, permanent faults from manufacturing defects, and aging-related deterioration. Developing comprehensive fault models and implementing effective redundancy and error correction techniques to address these scenarios is a complex, resourceintensive endeavor.

Another significant hurdle is the overhead linked to fault tolerance mechanisms. Techniques like Triple Modular Redundancy (TMR) and error-correcting codes (ECC) can substantially increase resource usage and power consumption of the FPGA. This overhead can be burdensome resource-constrained especially in environments, such as embedded systems and IoT devices. Balancing the trade-offs between fault power tolerance and system performance, consumption, and resource utilization is a delicate and ongoing challenge.

The dynamic aspect of reconfigurable architectures further complicates fault tolerance implementation. FPGAs are designed for on-the-fly reconfiguration to adapt to changing application needs or recover from faults. Managing this dynamic reconfiguration process to ensure minimal disruption and downtime requires sophisticated control algorithms and mechanisms. Ensuring the system can quickly detect faults, decide on the appropriate reconfiguration strategy, and implement it without compromising overall functionality is a complex problem.

Ensuring the reliability and validation of fault-tolerant reconfigurable systems poses additional challenges. Traditional testing and validation techniques often fall short for reconfigurable architectures due to their dynamic configurations [8]. Exhaustively testing and verifying all possible configurations for fault tolerance is impractical, creating potential reliability gaps. Developing new validation methodologies and tools that effectively handle the dynamic nature of reconfigurable systems is crucial for ensuring their reliability in real-world applications.

Finally, integrating fault tolerance mechanisms into existing design workflows and tools remains a challenge. Engineers need to incorporate fault tolerance seamlessly into their design processes without disrupting established practices. This requires the creation of new design tools and methodologies that support fault tolerance from the initial design stages through to implementation and verification. These tools must be user-friendly and provide clear guidance on best practices for implementing fault tolerance in reconfigurable architectures.

#### Case Studies and Applications of Fault Tolerance in Reconfigurable Systems

Fault tolerance in reconfigurable systems, particularly those using Field-Programmable Gate Arrays (FPGAs), is crucial across industries where reliability and continuous operation are critical. Two notable examples demonstrate how fault tolerance mechanisms are implemented and their effectiveness in reconfigurable computing.

In aerospace and defense applications, FPGAs with fault tolerance features are essential. For instance, in satellite systems, FPGAs handle real-time data processing, communication, and control tasks [9]. These systems face radiation in space, causing faults like single-event upsets (SEUs). To mitigate these risks, FPGAs use error detection and correction codes (EDAC), such as Triple Modular Redundancy (TMR). Critical circuits are triplicated, and outputs are cross-checked to detect and correct errors. This redundancy ensures that if one FPGA module fails, the system can continue functioning reliably without compromising mission objectives.

In industrial automation, fault-tolerant FPGAs enhance reliability and uptime. In manufacturing, where downtime leads to significant financial losses, these FPGAs are used in control systems for tasks such as real-time monitoring, process control, and machine vision [10]. Redundancy techniques ensure continuous operation despite potential hardware faults. Dynamic reconfiguration capabilities enable systems to adjust in real-time to production changes or bypass faulty components without stopping operations. This flexibility and resilience are crucial for maintaining productivity and efficiency in dynamic manufacturing environments.

These case studies underscore the effectiveness and versatility of fault tolerance mechanisms in reconfigurable systems across industries like aerospace, defense, and industrial automation. By integrating robust fault tolerance strategies into FPGA-based organizations designs, ensure high reliability, performance, and resilience against hardware faults, operation uninterrupted supporting in critical scenarios. Ongoing advancements in fault tolerance techniques and FPGA technology promise further improvements in reconfigurable systems' capabilities and applications.

## **Emerging Trends and Innovations**

Current trends in fault tolerance techniques for reconfigurable systems, especially those employing Field-Programmable Gate Arrays (FPGAs), focus on improving resilience, efficiency, and adaptability in dynamic computing environments.

One notable trend involves integrating machine learning (ML) and artificial intelligence (AI) algorithms with fault tolerance strategies. These technologies analyze system behavior in real-time, predict potential faults, and adjust fault tolerance measures dynamically. This proactive approach enhances system reliability by addressing issues preemptively, minimizing downtime, and ensuring continuous operation.

Another innovative trend is the implementation of selfhealing architectures in reconfigurable systems. These architectures enable automated detection, diagnosis, and mitigation of faults without human intervention. This capability is particularly beneficial in critical applications where rapid response and uninterrupted operation are crucial. By employing adaptive fault detection algorithms and autonomous reconfiguration strategies, self-healing architectures bolster system resilience and reduce maintenance requirements.

Advancements in hardware-based fault tolerance techniques are also shaping the future of reconfigurable computing. Techniques such as selective redundancy optimize resource utilization hv redundantly implementing critical components while streamlining non-critical ones for efficiency. Additionally, robust design methodologies incorporating resilient coding schemes and fault-tolerant circuits at the FPGA level ensure reliable operation, especially in environments prone to radiation-induced faults.

Furthermore, the development of standardized fault tolerance frameworks and design methodologies is facilitating wider adoption and interoperability of fault-tolerant reconfigurable systems. Standardized approaches streamline development processes, enable seamless integration of fault tolerance mechanisms into existing designs, and promote consistency in reliability across various applications and industries.

## **Conclusion and Future Directions**

In summary, fault tolerance remains a critical focus area for advancing reconfigurable computing systems, especially those using Field-Programmable Gate Arrays (FPGAs). The development of fault tolerance techniques has significantly improved the resilience and reliability of these systems in various demanding applications, such as aerospace, defense, and industrial automation. Through methods like redundancy, error correction, and adaptive reconfiguration, engineers have effectively minimized the impact of hardware faults and ensured continuous operation even in challenging environments.

Looking forward, future directions in fault tolerance for reconfigurable computing aim to innovate and refine existing methodologies further. One promising direction involves integrating advanced machine learning algorithms to enhance fault prediction and proactive fault management. By leveraging real-time data analysis and predictive models, reconfigurable systems can anticipate potential failures and autonomously take corrective actions, thus reducing downtime and optimizing overall system performance. Additionally, the evolution of self-healing architectures represents a transformative approach in fault tolerance. These architectures empower systems to autonomously detect, diagnose, and mitigate faults without human intervention, significantly enhancing operational efficiency and lowering maintenance costs. Advances in hardware-based fault tolerance techniques, such as enhanced redundancy and resilient design practices, will continue to play a pivotal role in strengthening system robustness and effectiveness.

Furthermore, efforts towards standardization in fault tolerance frameworks and design methodologies will facilitate broader adoption and interoperability of fault-tolerant reconfigurable systems across diverse industries. Establishing common standards and best practices will streamline development processes, ensure compatibility between hardware and software components, and stimulate innovation in fault tolerance solutions. Embracing these future directions and innovations will enable reconfigurable computing to further elevate its capacity in delivering reliable, resilient, and high-performance solutions for various applications and sectors.

#### REFERENCES

- [1] Jacobs, Adam, et al. "Reconfigurable fault tolerance: A comprehensive framework for reliable and adaptive FPGA-based space computing." ACM Transactions on Reconfigurable Technology and Systems (TRETS) 5.4 (2012): 1-30.

- [2] Khatri, Abdul Rafay. "Overview of fault tolerance techniques and the proposed TMR generator tool for FPGA designs." International Journal of Advanced Computer Science and Applications 11.4 (2020).

- [3] Rullo, Antonino, Edoardo Serra, and Jorge Lobo. "Redundancy as a measure of fault-tolerance for the Internet of Things: A review." Policy-Based Autonomic Data Governance (2019): 202-226.

- [4] Duddu, Vasisht, et al. "Fault tolerance of neural networks in adversarial settings." Journal of Intelligent & Fuzzy Systems 38.5 (2020): 5897-5907.

- [5] Rullo, Antonino, Edoardo Serra, and Jorge Lobo. "Redundancy as a measure of fault-tolerance for the Internet of Things: A review." Policy-Based Autonomic Data Governance (2019): 202-226.

- [6] Reyserhove, Hans, et al. "Error Detection and Correction." Efficient Design of Variation-Resilient Ultra-Low Energy Digital Processors (2019): 127-161.

- [7] Hauck, Scott, and Andre DeHon. Reconfigurable computing: the theory and practice of FPGA-based computation. Elsevier, 2010.

- [8] Koch, Dirk, et al. "Partial reconfiguration on FPGAs in practice—Tools and applications." ARCS 2012. IEEE, 2012.

- [9] Zolghadri, Ali, et al. Fault diagnosis and fult-tolerant control and guidance for aerospace vehicles. Vol. 236. London, UK:: Springer, 2014.

- [10] Oriol, Manuel, et al. "Fault-tolerant fault tolerance for component-based automation systems." Proceedings of the 4th international ACM Sigsoft symposium on Architecting critical systems. 2013.