**RESEARCH ARTICLE**

# Optimizing Reconfigurable Architectures for Enhanced Performance in Computing

#### Robbi Rahim

Sekolah Tinggi Ilmu Manajemen Sukma, Medan, Indonesia.

#### Abstract

Reconfigurable architectures have become a vital solution for boosting computational performance across various applications. Unlike traditional fixedfunction hardware, these architectures, such as Field-Programmable Gate Arrays (FPGAs), offer the capability to be dynamically reprogrammed to match specific computational needs, thus providing significant flexibility and efficiency. This paper delves into the essential techniques for optimizing these architectures, with a focus on methods to maximize throughput, reduce latency, and enhance energy efficiency. Through comprehensive case studies, we demonstrate the practical advantages and performance enhancements achieved by employing reconfigurable computing in domains like data processing, machine learning, and signal processing. The paper also examines the inherent challenges in optimization, such as the complexity of design and integration, and offers insights into emerging solutions and methodologies. Additionally, we provide a comparative analysis of various optimization strategies and discuss future trends that are expected to drive the evolution of reconfigurable computing, highlighting the potential for ongoing innovation and performance advancements in this ever-evolving field.

Author's e-mail: usurobbi85@zoho.com

How to cite this article: Robbi Rahim, Optimizing Reconfigurable Architectures for Enhanced Performance in Computing. SCCTS Transactions on Reconfigurable Computing, Vol. 1, No. 1, 2024 (pp. 11-15).

## INTRODUCTION

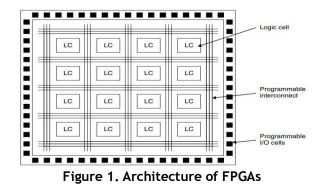

Reconfigurable architectures have become crucial in the pursuit of high-performance, energy-efficient, and versatile computing systems. Field-Programmable Gate Arrays (FPGAs) exemplify these architectures, offering a combination of flexibility and efficiency that fixedfunction processors cannot achieve. By allowing dynamic hardware reconfiguration tailored to specific applications, these architectures optimize performance in ways unattainable through software alone, meeting the increasing demands of diverse and computationally intensive tasks [1]. FPGAs architecture consists of programmable Logic Cells, programmable interconnects and programmable IO blocks is shown in Figure 1.

Field-Programmable Gate Arrays (FPGAs), Computational optimization, Performance enhancement.

#### ARTICLE HISTORY:

KEYWORDS:

Submitted:

01.02.2024

Revised:

16.02.2024

Accepted:

16.03.2024

Reconfigurable architectures,

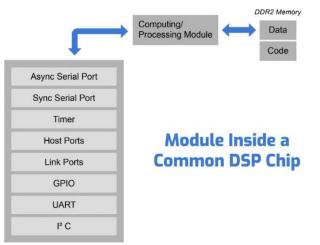

DOI: https://doi.org/10.31838/rcc/01.01.03 The essence of reconfigurable architectures lies in their programmability. Unlike conventional processors with fixed designs for general-purpose tasks, reconfigurable devices can be customized at the hardware level to perform specific functions. This is made possible through programmable logic blocks and interconnects, which can be reprogrammed to create different circuit configurations. This capability is particularly advantageous in applications where performance and power efficiency are critical, such as telecommunications, automotive systems, and data centers. One of the key strengths of reconfigurable architectures is their ability to accelerate computation by customizing the hardware to meet the needs of a particular application. For example, in digital signal processing (DSP) (Figure 2), FPGAs can be configured to execute parallel processing tasks more efficiently than general-purpose CPUs, resulting in faster speeds and lower power consumption [2]. This makes them ideal for real-time processing tasks in fields like image and video processing, where low latency and high power efficiency are crucial.

Figure 2. DSP Architecture

Moreover, reconfigurable architectures are highly adaptable. As technological advancements and application requirements evolve, the ability to reprogram hardware without needing a physical redesign offers a desirable level of future-proofing. This adaptability is especially significant in areas such as machine learning and artificial intelligence, where algorithms and models are continually evolving [3]. Reconfigurable architectures can be updated and optimized to keep pace with these changes, ensuring ongoing performance improvements.

Energy efficiency is another significant benefit of reconfigurable architectures. Traditional processors often face inefficiencies due to their general-purpose design, which is not optimized for specific tasks. In contrast, reconfigurable devices can be programmed to eliminate unnecessary processing steps and optimize data paths, leading to substantial power consumption reductions [4]. This is particularly important for battery-operated and portable devices, where energy efficiency directly translates to longer operational life and reduced heat generation.

In addition to performance and efficiency benefits, reconfigurable architectures also offer enhanced reliability and fault tolerance. They allow for the implementation of redundant circuits and dynamic reconfiguration, enabling continued operation even in the presence of hardware faults. This is critical in applications like aerospace and medical devices, where system failures can have severe consequences [5]. By reconfiguring the hardware to bypass faulty components, these architectures ensure higher reliability and robustness.

However, reconfigurable architectures also come with challenges. The complexity of design and programming is a primary obstacle. Efficient FPGA configurations require a deep understanding of both hardware and software design principles, along with proficiency in hardware description languages such as VHDL or Verilog [6]. This complexity can be a barrier for many developers and organizations, necessitating specialized tools and methodologies to simplify the design process.

performance advantages Moreover, the of reconfigurable architectures can be highly applicationspecific. While FPGAs excel in parallel processing and real-time applications, they may not always offer significant benefits for tasks requiring complex control logic high-precision arithmetic or operations. Therefore, careful consideration and evaluation are necessary to determine the suitability of reconfigurable architectures for a given application, balancing the trade-offs between performance, power consumption, and design complexity.

In summary, reconfigurable architectures represent a significant shift in computing, offering unmatched flexibility, performance, and efficiency. Their ability to adapt to changing requirements and optimize hardware for specific tasks makes them invaluable in a wide

range of applications, from consumer electronics to critical infrastructure. As the demand for highperformance and energy-efficient computing continues to rise, reconfigurable architectures are set to play a pivotal role in the future of technology, driving innovation and enabling new possibilities across various domains.

## Key Techniques for Performance Optimization

Optimizing performance in reconfigurable computing architectures, particularly those employing Field-Programmable Gate Arrays (FPGAs), requires a blend of hardware and software strategies. These techniques are crucial for enhancing efficiency, speed, and overall computational effectiveness [7]. Here are some key methods for performance optimization in reconfigurable architectures:

One of the core advantages of reconfigurable architectures is their ability to exploit parallelism. By distributing computations across multiple processing units, tasks can be executed concurrently, significantly improving performance. FPGAs excel in this area as they can be programmed to run numerous operations simultaneously. Additionally, pipelining is a critical technique where different stages of computation are overlapped. This allows one stage to process data while the next stage simultaneously begins processing the output of the previous stage, thereby reducing latency and increasing throughput.

Creating custom instruction sets tailored to specific applications can also enhance performance. In reconfigurable architectures, designers can implement specialized instructions that accelerate common or computationally intensive tasks. This customization reduces the number of instructions needed to perform a task, thus speeding up execution and improving efficiency. These custom instructions are designed to handle specific operations more efficiently than general-purpose instructions.

Efficient resource allocation and scheduling are essential for optimizing performance. This involves strategically assigning computational resources to various tasks to ensure that critical paths are optimized and resources are utilized effectively. Advanced scheduling algorithms can dynamically adjust the allocation of resources based on the workload, ensuring optimal performance under varying conditions. This dynamic adjustment helps in balancing the load and preventing bottlenecks.

Memory access and bandwidth often become high-performance bottlenecks in computing. Techniques such as data prefetching, efficient memory hierarchies, and minimizing memory access latency are crucial. By optimizing memory usage and ensuring data availability when needed, reconfigurable architectures can significantly enhance performance. Utilizing onchip memory resources like Block RAM (BRAM) in FPGAs can reduce reliance on slower off-chip memory, thus speeding up data access and processing.

Dynamic reconfiguration is another unique advantage of reconfigurable architectures. This capability allows specific parts of an FPGA to be reconfigured while the rest of the device continues to operate. Dynamic partial reconfiguration enables the system to adapt to changing workloads and optimize performance for different tasks in real time without downtime. Advanced tools and frameworks designed for FPGA and reconfigurable architectures also streamline the optimization process. High-level synthesis (HLS) tools allow designers to describe algorithms in high-level programming languages, which are then automatically translated into optimized hardware descriptions. These tools reduce design complexity and enhance performance by automating many optimization processes.

## **Case Studies and Applications**

Reconfigurable architectures, especially those utilizing Field-Programmable Gate Arrays (FPGAs), have become pivotal across various industries due to their flexibility and performance advantages. These architectures have been implemented in real-world scenarios, demonstrating their capability to meet specific computational requirements more effectively than traditional fixed architectures.

In the realm of high-frequency trading (HFT), for example, where ultra-low latency is critical for exploiting rapid market changes, FPGAs have proven invaluable. Financial firms deploy FPGAs to execute custom trading algorithms directly in hardware, significantly reducing processing times compared to software running on general-purpose CPUs [8]. This hardware-level execution speeds up trading operations and enhances overall system efficiency by lowering power consumption.

Telecommunications also benefits significantly from FPGAs, particularly in real-time signal processing applications. With the advent of technologies like 5G demanding high data rates and minimal latency, FPGAs enable implementation of complex signal the processing algorithms directly in hardware. This capability ensures faster data processing and transmission, thereby improving the performance and reliability of communication networks [9]. Base stations equipped with FPGAs can dynamically adjust to fluctuating traffic and environmental conditions, ensuring optimal network operation and signal quality. In the automotive sector, reconfigurable architectures are crucial for advanced driver-assistance systems (ADAS) and autonomous driving technologies. These systems rely on real-time processing of extensive sensor data, including images and radar signals [10]. FPGAs enable efficient implementation of deep learning algorithms for object detection and recognition, allowing vehicles to make quick decisions in complex driving scenarios. The flexibility of FPGAs also facilitates seamless updates and enhancements to ADAS features as new algorithms and sensors are

developed.

In healthcare, reconfigurable computing plays a pivotal role in medical imaging systems such as MRI and CT scanners. These systems require high-speed data processing for accurate image reconstruction, which FPGAs can accelerate, reducing scan times and improving diagnostic accuracy. Portable medical devices also utilize FPGAs for real-time monitoring and analysis of vital signs, delivering timely health information to patients and healthcare providers [11]. The adaptability of FPGAs enables integration of new diagnostic algorithms and techniques without requiring hardware replacements.

These case studies underscore the versatility and effectiveness of reconfigurable architectures in addressing diverse and demanding computational challenges. FPGAs and similar technologies offer significant performance enhancements, lower latency, and greater adaptability, making them indispensable in fields requiring specialized and high-performance computing solutions.

### **Challenges and Solutions in Optimization**

Optimizing reconfigurable architectures, particularly Field-Programmable Gate Arrays (FPGAs), involves overcoming several challenges and implementing innovative solutions to achieve maximum performance and efficiency across diverse applications.

One significant hurdle is the complexity inherent in hardware design and FPGA programming. Unlike conventional software development on CPUs, FPGA programming requires expertise in hardware description languages (HDLs) like Verilog and VHDL. This complexity can hinder widespread adoption and effective utilization of FPGA resources, particularly for developers who lack specialized hardware design skills. Another critical challenge is ensuring optimal use of FPGA resources and achieving desired performance levels. FPGAs provide configurable logic blocks (CLBs), memory elements, and DSP slices that must be efficiently allocated to execute tasks with high parallelism while minimizing resource conflicts. Careful partitioning of algorithms and tasks is essential to fully exploit FPGA capabilities without exceeding resource limits.

Compatibility and integration with existing software environments pose additional complexities. Seamless interaction between FPGA-based accelerators and host systems requires robust communication protocols and custom interfaces. Developing drivers and software frameworks that facilitate efficient data exchange and synchronization between FPGA hardware and software components is crucial for seamless integration.

Effective management of power consumption and heat dissipation presents another significant challenge in FPGA optimization. While FPGAs offer superior performance, they can consume substantial power, especially under heavy computational workloads. Implementing strategies such as dynamic voltage and frequency scaling (DVFS) and power gating helps minimize energy usage and mitigate thermal issues, thereby enhancing reliability and extending FPGA lifespan.

Addressing these challenges necessitates а comprehensive approach that combines advanced methodologies, hardware design optimized programming techniques, and efficient power management strategies. Simplifying FPGA programming tools and environments can democratize access to FPGA technology, making it more accessible across various industries. Ongoing research into new FPGA architectures and optimization algorithms continues to drive advancements, pushing the boundaries of performance and efficiency in reconfigurable computing systems.

### **Future Directions in Reconfigurable Computing**

Looking forward, the future of reconfigurable computing is poised for significant advancements across various fields driven by ongoing research and innovation. A key area of focus is the development of more efficient and flexible FPGA architectures designed to meet the growing demands of modern applications. These architectures aim to improve scalability, performance, and resource utilization, catering to complex computations and accelerating tasks from AI inference to real-time data processing. Integration with emerging technologies like edge computing and IoT devices represents another critical growth area. FPGAs are set to play a pivotal role in edge devices by enabling on-device processing of large datasets, reducing latency, and enhancing privacy and security. This integration is crucial for applications requiring rapid decision-making and responsiveness, such as autonomous vehicles, smart sensors, and industrial automation.

Advancements in development tools and methodologies for FPGA design are also anticipated to streamline the development process and lower entry barriers for developers. Simplified programming environments, high-level synthesis tools, and improved debugging capabilities will empower software engineers and domain experts to harness FPGA capabilities more effectively, driving innovation across sectors such as healthcare, finance, and telecommunications.

#### REFERENCES

- [1] Maxfield, Clive. The design warrior's guide to FPGAs: devices, tools and flows. Elsevier, 2004.

- [2] Tessier, Russell, and Wayne Burleson. "Reconfigurable computing for digital signal processing: A survey." Journal of VLSI signal processing systems for signal, image and video technology 28 (2001): 7-27.

- [3] Compton, Katherine, and Scott Hauck. "Reconfigurable computing: a survey of systems and software." ACM Computing Surveys (csuR) 34.2 (2002): 171-210.

- [4] Huang, Chongwen, et al. "Reconfigurable intelligent surfaces for energy efficiency in wireless communication." IEEE transactions on wireless communications 18.8 (2019): 4157-4170.

- [5] Kubatova, Hana, and Pavel Kubalik. "Fault-tolerant and fail-safe design based on reconfiguration." Design and

Test Technology for Dependable Systems-on-Chip. IGI Global, 2011. 175-194.

- [6] Lyke, James C., et al. "An introduction to reconfigurable systems." Proceedings of the IEEE 103.3 (2015): 291-317.

- [7] Hauck, Scott, and Andre DeHon. Reconfigurable computing: the theory and practice of FPGA-based computation. Elsevier, 2010.

- [8] Leber, Christian, Benjamin Geib, and Heiner Litz. "High frequency trading acceleration using FPGAs." 2011 21st International Conference on Field Programmable Logic and Applications. IEEE, 2011.

- [9] Rao, Raghu M., Mickaël Fontaine, and RaimenaVeisllari. "A reconfigurable architecture for packet based 5G transport networks." 2018 IEEE 5G World Forum (5GWF). IEEE, 2018.

- [10] Chaudhary, Vikas. "Reconfigurable computing for smart vehicles." Smart Cities: Applications, Technologies, Standards, and Driving Factors (2018): 135-147.

- [11] Alcaín, Eduardo, et al. "Hardware architectures for realtime medical imaging." Electronics 10.24 (2021): 3118.