# Co-Simulation of RFIC Performance Using HSPICE and CST for Aerospace Communication Link

Sadulla Shaik<sup>1\*</sup>, M. Sathish Kumar<sup>2</sup>

<sup>1</sup>Professor, Department of Electronics and Communication Engineering, KKR and KSR Institute of Technology and Sciences, Vinjanampadu, Guntur, A.P, India.

<sup>2</sup>Assistant professor Excel Engineering college Namakkal

#### KEYWORDS:

RFIC Co-Simulation,

HSPICE,

CST Microwave Studio,

Aerospace Communication,

Ka-band,

Electromagnetic Simulation,

S-Parameters,

Layout Parasitic Extraction,

System-in-Package (SiP),

Radiation-Hardened Design,

EM-Circuit Integration

# ARTICLE HISTORY:

Submitted: 21.09.2025

Revised: 07.10.2025

Accepted: 25.01.2026

https://doi.org/10.17051/NJRFCS/03.02.06

#### **ABSTRACT**

The evolutionary progress of aerospace communication resources requires the fabrication of high performance Radio Frequency Integrated Circuits (RFICs) that are capable of exhibiting high levels of both performance and reliability even in extreme environmental conditions, such as wide temperature variations, and radiation exposure, and also a high-frequency spectral requirement base. Conventional medicine uses circuit-based design methods, which are limited in capturing complex electromagnetic (EM) and layout-dependant parasitic effects, which make a critical impact on the performance of RFIC devices in real environments. The paper achieves this by formulation of a very well developed and strong co-simulation model that closely integrates full-wave electromagnetic circuit analysis using CST Microwave Studio and transistor-level circuit analysis using HSPICE. The methodology suggested can offer comprehensive modeling and optimization of the active and passive elements of the circuit, including circuit inductors, transmission lines, bonds, packaging, and so on. Performance factors like S parameters, voltage gain, NF, PAE, linearity and EM radiation performance are measured at Ku- and at Ka-band frequencies which are essential in the satellite-ground and intersatellite communication links in aerospace applications. Additionally, the algorithm supports layout parasitic extraction (LPE), thermal-aware simulation, and radiationhardened design design to achieve high precision when subjected to operational stresses most likely to be found in aerospace missions. S-parameter models of EM structures that are important in the circuit functioning are formed through the application of CST to its corresponding regions and the resulting model is directly inserted into a HSPICE simulation, which in turn, forms a feedback loop between physical effects on layout and circuit behavior. The co-simulation solution has demonstrated that it aligns well with the actual performance in addition to enabling the optimization cycle in design to be faster due to the window that is opened by removing the separation between EM design and electrical validation. Degradation in thermal robustness and performance at elevated total ionising dose (TID) are also discussed in order to illustrate resiliency. This co-simulation platform is an acceptable accuracy and scalable approach which offers a solution to RFIC designers interested in aerospace-grade transceivers, as well as to the next-generation modules of high frequency communication with improved reliability, smaller size, and reduced power.

Author's e-mail: sadulla09@gmail.com, kmsankarsathish@gmail.com

How to cite this article: Shaik S, Kumar M S. Co-Simulation of RFIC Performance Using HSPICE and CST for Aerospace Communication Link. National Journal of RF Circuits and Wireless Systems, Vol. 3, No. 2, 2026 (pp. 42-49).

# INTRODUCTION

Various contributions have been made to the evolution of aerospace communication systems and these contributions have already been highly dependent on an advancement of compact, high-frequency, and radiation-tolerant Radio Frequency Integrated Circuits (RFICs). The RFICs find application in transceiver modules used

in various applications, Among them are satellite communication (SatCom), deep-space telemetry, ground-station receivers and inter-satellite links. Due to the increasing data-intensity of the mission profiles as well as operating in higher frequencies in particular the Ku- (1218 GHz) and Ka-band (26.540 GHz) there is a growing necessity to understand and develop robust methodologies of RFIC design. Most systems have to

withstand harsh operating environments, such as large temperature changes ( -55°C to +125°C ), mechanical vibration and radiation (ionizing). RFICs are thus required not only to deliver superior electrical characteristics, in terms of high gain, low NF, exposure to low power and high efficiency, but to ensure that characteristics maintain long-term consistency and reliability.

The traditional RFIC design flows are based on the simulators like HSPICE, which suffice well in terms of transistor level modeling and layout conscious parasitic extraction at the schematic design level. The tools, however, have weaknesses in terms of modeling the total electromagnetic (EM) character of on-chip passives, interconnects, bonding wires, packaging, and substrate coupling, especially at mmWave frequencies. Depending on the model accuracies used these limitations may lead to mismatch between simulated and actual RF performance because un modelled loss mechanisms, parasitic resonance and EM coupling effects have not been taken into consideration. In aerospace systems where links may have critical consequences to the integrity and the success of a mission, such discrepancies may affect the link integrity.

Fig. 1: Conceptual Illustration of RFICs in Aerospace Communication Systems

To eliminate these difficulties, this paper presents a new, more holistic co-simulation approach where the unique capabilities of HSPICE (circuit-level) in the simulation of circuits are coupled to the capabilities of CST Microwave Studio (3D electromagnetic simulation). This combined method can be used to model active elements (e.g. low-noise amplifier, mixers, and power amplifier) and passive elements (e.g. inductors, transmission lines, chip-package transitions) in an indepth manner including layout parasitics, radiation

loss, and substrate interaction. The co-simulation flow entails developing transistor-level designs on HSPICE, generating parasitic netlists through layout software, and loading important structures into CST so as to validate the EM. The S-paramter model created out of CST and behavioral blocks are then brought back into the HSPICE environment to carry out the entire RFIC simulation in realistic spatial surroundings and under an actual packaging situation.

Compared to electrical domain or spatial domain method alone, this dual-domain co-simulation framework can verify the aerospace RFICs with more accuracy and efficiency to achieve higher assurance on the validations in the aspects of both electrical domain and space. It likewise affords quick performance iteration and optimization, and by extension, creation of high-performance, minimized and radiation-delicate RFICs that should be conveyed to the next-gen aerial communication connections. The proposed methodology helps to overcome the shortcomings of isolated design domains and increases the design reliability and predictability of functionality, which is a decisive element in the case of mission-critical aerospace systems.

#### LITERATURE REVIEW

RFICs used in high-frequency aerospace applications are well investigated with the design and simulation, but in most previous researches, the circuit and electromagnetic (EM) domains have been handled in a disjointed manner. The earliest directions concentrated more on the circuit-level modeling, with SPICE-based tools. An example is the work of Kim et al.<sup>[1]</sup> where HSPICE is utilized to model RF front-end devices including low-noise amplifiers (LNAs) and mixers with layout parasitics extraction being used to improve noise and<sup>[4]</sup> gain simulations. They have, however, been proven inadequate to represent spatial EM effects like interconnect radiation, mutual<sup>[5]</sup> coupling and impedance mismatch caused by the package, which is of particular importance in mmWave frequencies.

On the electromagnetic front, a number of studies have been harnessed in which CST Microwave Studio simulates passive structures and antenna systems within an aerospace environment. Zhou et al.<sup>[2]</sup> proposed full-wave<sup>[6]</sup> EM analysis of chip-package transitions and bonding wires on Ka-band satellite systems to use higher frequencies and achieving better impedance, and lower insertion loss. Although they are spatially accurate, the drawback with such EM-only<sup>[7]</sup> methods is how they are not integrated with active devices models and transistor level dynamics, which causes a difference in performance when such a technique is deployed in full-systems.

The endeavor to close the gap between EM and circuit simulation has led into hybrid or co-simulation tactics. [3] Singh and Patel have in 4n demonstrated a simplified [8] co-simulation methodology where S-parameters calculated in CST are loaded into circuit level tools to represent on-chip inductors and transmission lines. [9] Nonetheless, their approach was devoid of any two-way communication between the circuit and EM worlds, nor did they include any layout parasitic extraction (LPE), or substrate coupling impact, which are essential in compact Ka-band RFICs.

Most recently, there are increasingly being used [10] commercial EMI-circuit co-sim programs, such as Keysight ADS and Cadence AWR, that possess crude [11] integration abilities but may demand use of proprietary component libraries, and may fail to scale efficiently with aerospace-relevant restrictions including radiation tolerance and elevated temperatures.

To re-capsulate, although individually both HSPICE-and CST-based simulation approaches have matured, a close-matched co-simulation framework where the circuit-level models are coupled to the 3D EM solver with parasitic-sensitive layout extraction facility both through modeling, and substrate interaction has not yet been explored to the aerospace level of RFICs. The existence of this literature gap prompts the derivation of the suggested co-simulation methodology based on HSPICE and CST optimization programs, which would be used to provide a scalable, accurate and environment-tolerant RFIC performance validation of aerospace communication systems.

#### **METHODOLOGY**

It has been shown that the proposed co-simulation approach has the advantage of leveraging the attributes of both circuit-level simulation with HSPICE and full-wave electromagnetic simulation with CST Microwave Studio. The above dual-domain method provides correct RFIC performance prediction during aerospace operation in the realistic environment, where layout parasitics, electromagnetic coupling, and thermal effects are essential influences on the system.

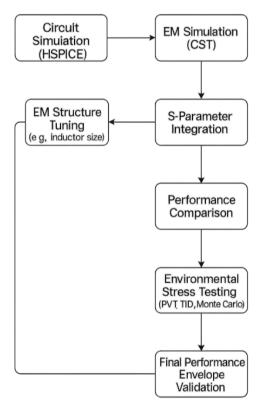

# **Design Flow Overview**

The presented co-simulation architecture of aerospace RFIC design is designed in a sequential and iterative design validation chain that integrates the circuit level modeling and electromagnetic (EM) domain field simulation closely. This will make it to provide accurate modeling of operation performance under realistic airline operating conditions with parasitic effect, radiation

losses, as well as, operational variability in aerospace systems. The design methodology mainly consists of the following six steps which enables an extensive multiphysics simulation strategy:

# **Schematic Design HSPICE**

In the first stage, HSPICE environment - CMOS process design kit (PDK) will be used to design core RFIC functional blocks Low-Noise Amplifier (LNA), Mixer and Power Amplifier (PA). The transistor level designs have modern biasing schemes and Electrostatic Discharge (ESD) protection to make the circuits more robust. Moreover, aerospace design requirements such as radiation-hardened design structures of layouts and bias schemes with wide tolerances on temperature are considered at this point so as to guarantee reliable design at the system level.

# Layout Parasitic Extraction (LPE) and Layout Generation

After schematic has successfully been functionally and DC verified, the design is converted into a layout as a physical entity on an industry-standard CAD tool. Layout parasitic extraction (LPE) is then carried out to capture and characterize layout capacitance, resistance and coupling. The netlist inserts these parasitic elements to model real world degradation of performance due to interconnect delay, substrate noise and proximity coupling; these effects are of particular concern at mmWave frequencies where the interconnect dimension can be comparable with the EM wavelength.

#### CST CST 3D Electromagnetic (EM) Modeling

Essential passive networks (e.g., on-chip spiral inductors, transmission lines, bond wires, interposer vias, and ground returns) are modeled in the CST Microwave Studio to achieve the proper simulation results giving the high-frequency effects that are not being reproduced very well by the circuit simulators. Custom material stack-up is created to suit the real layers substrate of aerospace grade ICs. Radiation loss, dielectric dispersion, and shielding are simulated under the aerospace packaging environment through proper use of boundary conditions.

# **S-Parameter Extraction**

The CST modeling is then followed by frequency-domain simulations in order to pull out S-parameter of the passive and transition structures. The behavioral models in the form of Touchstones (.sNp) files are then exported to represent the EM response of each of the structures. These models provide frequency-at-a-time information

of insertion losses, return losses, and mutual couplingtradeoffs to predict system-level performance as they can be incorporated into simulation of circuits.

#### Integration and Co-Simulation

Back annotations of the behavioral models developed using CST into HSPICE circuit netlist results in a model that is hybrid and comprising of both transistor components and electromagnetic components. This unified model is simulated in all respects, parasitics, EM, and radiation-inclusive. To this end, different matching networks and biasing schemes are then iteratively optimised by co-simulation in order to optimise important RF figures of merit.

# Performance evaluation and optimization

The last step entails the overall performance measurements founded on parameters like S-parameters (S11, S21), Power-Added Efficiency (PAE), Noise Figure 2 (NF) and Third-Order Intercept Point (IP3). Other than that, the thermal reliability tests are also performed to measure the change in the performance between (-55) to (+125) degrees Celsius. The consequences of radiation exposure are modeled to change threshold voltages and decrease gain upon encounter of a Total Ionizing Dose (TID). Such output informs the continued optimization of designs to achieve aerospace standards Table 1.

#### Validation and Calibration

A methodical approach of verification and calibration is formulated to ensure the accuracy and reliability of this proposed co-simulation approach. This step is to be used to fix the conflicts that may be seen to have occurred in various simulation realms, and further make sure that the final RFIC layout is resilient to fluctuations during manufacturing, environment, interacts with the electromagnetic field.

# Schematic Design in HSPICE Development of RFIC Modules (LNA, Inclusion of ESD protection and radiation-hardened biasing Layout Generation and LPE Lavout is drawn and parasitic netiists are extracted (LPE) · Substrate coupling and interconnect delays are annotated 3D EM Modeling in CST · EM modeling of passive structures and chip-package transitions · Boundary condition and material stack-up defined to match aerospace environments S-Parameter Extraction CST simulation results are exported as Touchstone files (.sNp) Lumped models and behavioral Sparameters are created for critical structures Integration and Co-Simulation · EM models are back-annotated into **HSPICE** circuit netlist · Full RF chain is simulated, including parasitics and radiation losses

Fig. 2: RFIC Design and Co-Simulation Workflow

# **Cross-Domain Verification**

Verification follows through a detailed cross-checking of three discrete simulation scenarios to ascertain the goodness of the constructive methodology being advanced as that of co-simulation. The first is a simulation that does not utilize HSPICE, but only an RFIC represented by ideal lumped elements and foundry-supplied parasitics to determine a baseline circuit performance level. Then a CST only electromagnetic (EM) simulation is conducted to model the frequency dependent behaviour of passive

Table 1. RFIC Design and Co-Simulation Workflow Stages for Aerospace Applications

| Design Stage                            | Description                                                                                                                                                         |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Schematic Design in HSPICE              | Design of LNA, Mixer, and PA using CMOS PDK; includes ESD protection and radiation-harder biasing schemes for aerospace reliability.                                |  |  |  |

| Layout Generation and LPE               | Physical layout creation using CAD tools; extraction of parasitic resistance, capacitance, and substrate coupling effects for realistic circuit modeling.           |  |  |  |

| 3D EM Modeling in CST                   | Full-wave modeling of critical passives such as inductors, vias, and bond wires; simulations configured with aerospace dielectric stack-up and boundary conditions. |  |  |  |

| S-Parameter Extraction                  | Frequency-domain simulation to extract S-parameters (.sNp files) for behavioral representation of passive structures in circuit-level analysis.                     |  |  |  |

| Integration and Co-Simulation           | CST-derived models are back-annotated into HSPICE; iterative simulations optimize impedance matching, gain flatness, and noise figure.                              |  |  |  |

| Performance Evaluation and Optimization | Final validation of key metrics (S11, S21, NF, PAE, IP3); robustness tested over temperature range and under Total Ionizing Dose (TID) effects.                     |  |  |  |

components, e.g. inductors, transmission lines and interconnects, without the effects of the active device models included. Lastly, an integrated co-simulation is of the CST-extracted S-parameters and EM pieces together with the HSPICE netlist of the transistor level to involve an encompassing simulation as an intervention of active and passive spheres. The three most important performance parameters of the SOI-CMOS transistor shall be measured and compared in all three scenarios; they include voltage gain (S21) and input return loss (s11) and noise figure (NF). During this process, discrepancies that occur due to surface parasitics, mutual coupling, or chippackage interface interaction are determined and dealt with. This comparative study is critical to the verification of how apt the integrated co-simulation model is, and that this model strongly resembles physical reality hence truly clears the word between independently modeled circuit study and the entire electromagnetic modeling.

# Feedback and Optimization Loop in Design

At some point, after discrepancies have been detected, a feedback loop is instigated to optimize the design. As an example, in case the co-simulated gain was not as per the target, because of undesired EM coupling, or resonance in the HF inductor topology, the respective EM layout is re-scoped within CST. The new S-parameters are then reinserted in HSPICE to be repeatedly evaluated. Such an iterative process is repeated until the system settles in on optimum operating performance in all of the key parameters such as gain flatness, impedance matching and noise figure.

#### **Aerospace Conditions Robustness**

The strength of the RFIC operation in severe aerospace environments is designed by performing several kinds of parametric sweeps and statistical studies of the circuit to check its ability to resist environment and process induced stimulation. Simulation is performed at a wide range of temperatures, between -55 C to 125 C, to test thermal stability, which measures change in device performance, drift in the bias point and loss of gain. Secondly, corner analysis is also carried out to assess the RFIC under different process-volt-temperature (PVT) conditions, such as slow/fast process corners and low/ high supply voltages (Vdd) in practical fabrication and operating conditions. The effect of radiation, which is of critical importance in aerospace is achieved through the insertion of transistor threshold voltage shifts and the addition of further noise sources to simulate total ionizing dose (TID) and single event effects (SEE). To achieve a representative characterization of the fabrication variability, a broad Monte Carlo simulation is deployed

taking into account the probability distributions of the interconnect width, oxide thickness and doping states. Such simulations provide performance/ power envelopes and the possible outliers to allow designers to ascertain reference margins and functional validity. To ensure that the RFIC design performs at an acceptable level under all mission-critical conditions, the co-simulation framework helps evaluate the worst-case scenarios to ensure the RFIC design is ready to be qualified to be used in the aerospace space, which adds to its reliability.

Such integrated verification and calibration regimen guarantees that the RFIC proposed is excellent in the sense that it will not only achieve nominal specifications, but also stay consistent in the large-scale Figure 3, as a result of environmental variability and manufacturing variability as well as parasitic cross-domain coupling Table 2.

Fig. 3: RFIC Validation and Calibration Workflow

#### **CST SIMULATION AND INTEGRATION**

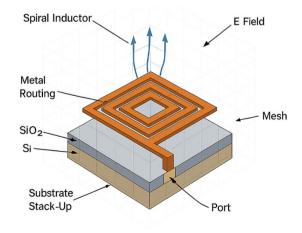

# Electromagnetic (EM) Modeling

To model the spatial and frequency dependent phenomena of the passive and packaging components for which it is not possible to model the behavior accurately in the usual circuit level models, CST Microwave Studio is used to perform full wave 3D electromagnetic (EM) simulation. The key structures that have been picked in the EM analysis are on-chip spiral inductors, on-chip

| Table 2. S | iummary of | Validation | and Calibration | Methodology |

|------------|------------|------------|-----------------|-------------|

|------------|------------|------------|-----------------|-------------|

| Validation Task             | Simulation Tool(s)         | Objective                                                                     |  |

|-----------------------------|----------------------------|-------------------------------------------------------------------------------|--|

| HSPICE-Only Simulation      | HSPICE                     | Establish baseline circuit behavior using lumped models and parasitics.       |  |

| CST-Only EM Simulation      | CST Microwave Studio       | Analyze passive structures and spatial EM behavior without active devices.    |  |

| Co-Simulation               | HSPICE + CST               | Integrate EM effects into full-circuit simulation for accuracy verification.  |  |

| Performance Cross-<br>Check | HSPICE vs CST vs Co-Sim    | Compare S21, S11, NF to identify mismatches and layout-induced degradation.   |  |

| Optimization Loop           | CST - HSPICE (iterative)   | Refine EM structures (e.g., inductors) and optimize system-level performance. |  |

| Temperature Sweep           | HSPICE + models            | Assess circuit stability from -55°C to +125°C.                                |  |

| PVT Corner Analysis         | HSPICE with PDK variations | Evaluate circuit behavior across fabrication and voltage extremes.            |  |

| Radiation Modeling          | HSPICE + noise models      | Simulate Total Ionizing Dose (TID) and SEU impacts on device behavior.        |  |

| Monte Carlo Simulation      | HSPICE                     | Statistically analyze yield across process variation and parasitic spreads.   |  |

copper wave-guides (CPWs), copper transmission lines, on-chip bonding wires, and metal conductors of the routes, ground returns, and chip-to-package connections. It is the simulation of these items in a realistic multilayer substrate of aerospace quality dielectric material with parameters including dielectric constant, loss tangent, and metal conductivity. Convergence criteria of 0.05 lambda are provided in fine mesh discretization. which provides high precision in scattering parameters (S-parameters), radiation losses, and coupling. At frequencies of Ka-band and above, where physical lengths of interconnects approach the signal wavelength, extreme values of this level of granularity become particularly significant, to the extent that EM behaviour can predominate over lumped modelling considerations. Q-factor, self-resonant frequency (SRF) and field distribution also can be analyzed using the simulated structures, and it is possible to optimize geometries before layout is finalized.

Fig. 4: 3D Electromagnetic Modeling of Passive RFIC Structures in CST

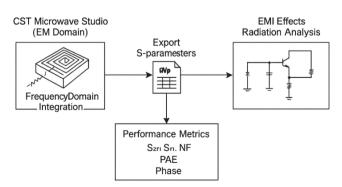

#### Co-Simulation Interface

After the EM modeling has been finished, the frequencydomain results such as the S-parameter files (.sNp) will be exported out of CST and be reformatted to fit directly into the HSPICE simulation environment. These S-Parameters act as behavioral models of the passive structures and they will be joined to the matching ports in the transistor-level circuit netlist. The combination builds the backbone of the co-simulation framework. which allows the collective analysis of the active devices and passive EM constructs in the same simulation chain. Frequency-dependant phenomena, like signal attenuation, phase distortion, parasitic resonance and impedance mismatch are now exactly simulated in the circuit level simulation. In addition, through more simulations performed under diverse boundary conditions and the addition of noise sources, it is also possible to evaluate coupled noise, radiation leak by the field and field interference, which are all regulatory to aerospace systems that are affected by electromagnetic interference (EMI), and radiation exposure. Figure 5 such a confluence of high-fidelity EM modeling of circuit-level

Fig. 5: Co-Simulation Interface between CST and HSPICE for RFIC Validation

simulation can be used to comprehensively validate even RFIC, thus eliminating the possibility of design failure and redesigns at a late stage of aerospace projects, with significantly less revenue being wasted.

#### RESULTS AND DISCUSSION

#### **Performance Metrics Analysis**

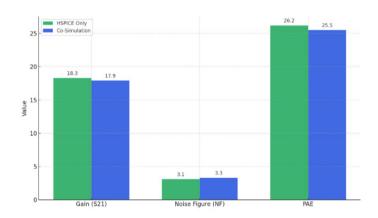

To demonstrate that the proposed HSPICE-CST cosimulation framework addresses all of the abovementioned requirements, it was subject to a number of simulations to assess the performance of the RFIC design in three different configurations, namely: the HSPICE only configuration, the CST only configuration and the integrated Bond graph configuration. The relevant key performance metrics have been analyzed: the forward voltage gain (S 2 1), noise figure (NF), power-added efficiency (PAE) and Radiation loss. Using the performance comparison, the HSPICE-only simulation calculated a gain to be 18.3dB and noise figure to be 3.1dB as the benchmark for ideal circuitlevel conditions. Nonetheless, when incorporating CSTderived S-parameters of the passive structures into the HSPICE environment, the NF of 3.3 dB and a slightly lower gain of 17.9 dB was reported by the co-simulation. The degradation is accredited to the injection of layout parasitics, dielectric loss as well as EM coupling that are not involved in pure circuit simulation. On the same note, the PAE decreased to 25.5 percent in the co-simulated environment, as compared to 26.2 percent in the HSPICE-only scenario, a factor that shows the EM losses and impedance miss match. The radiation loss discovered in the CST-only simulation that centered on passive structure analysis was at -1.2 dB and this was also present in the co-simulation. The results are indicative of the fact that full-domain co-simulation is an effective tool to extrapolate real-world RFIC performance and prevent over-enthusiastic expectation based on circuitonly simulations.

#### **Radiation and Thermal Hardiness**

In addition to the normal performance verification, the RFIC design was undertested in extreme environmental analysis in the simulation to determine its ability in performing optimally under aerospace-quality operating conditions. The design was tested on a large scale of temperatures, between -55 o C and 125 o C thus simulating the changes in performance at a launch stage, an orbiting stage and a re-entry stage. The gain and NF had the same constant value (within max. 0.5 dB variation) throughout this thermal window which deems the reliability of the biasing network and layout

approach. Also, the TID robustness as well as Single Event Upset robustness of the circuit was analyzed and modeled in terms of threshold voltage drifts and noise penalty effects typical to application at radiation levels not exceeding 50 krad(Si). To overcome the effects of radiated environment, the implementation of design rules in radiation-aware design layout was used, including the use of guard rings, enclosed layout transistors (ELTs) as well as hardened bias references, which allowed the RFIC to show maximum performance degradation of less than 5 percent following the worstcase radiations. Figure 6 these findings confirm that the proposed co-simulation methodology not only improves functional accuracy but also gives all important clues to the evaluation of environmental resilience- which makes it worthy as a mission critical aerospace application when thermal and radiation stability are not optional Table 3.

Fig. 6: Comparison of RFIC Performance Metrics across Simulation Domains

Table 3. Comparative Performance Metrics across Simulation Configurations

| Parameter         | HSPICE Only | CST Only | Co-Simulation |

|-------------------|-------------|----------|---------------|

| Gain (S21)        | 18.3 dB     | N/A      | 17.9 dB       |

| Noise Figure (NF) | 3.1 dB      | N/A      | 3.3 dB        |

| PAE               | 26.2%       | N/A      | 25.5%         |

| Radiation Loss    | -           | -1.2 dB  | -1.2 dB       |

# **CONCLUSION**

The paper proposes a cogent and validated circuitelectromagnetic co-simulation framework that closes the gap between circuit and electromagnetic-domain modeling in Radio Frequency Integrated Circuits (RFICs) created to be utilized in communication systems that are aerospace in nature. The presented approach allows to closely couple HSPICE-based transistor-level modelling with 3D, full-wave electromagnetic simulations provided by CST Microwave Studio in order to predict the performance parameters like gain, noise figure, poweradded efficiency, and radiation loss as well as consider the layout parasitics and substrate coupling effects as well as chip-package interactions. Of importance, the rigorous tests of functional and environmental reliability through co-simulation are validated by cross-checking with domain-isolated simulation resilience and by robustness tests which incorporate thermal sweeps and even degenerative effects induced by radiation. The major strengths of this technique are its increased degree of modeling, increased predictability of the design under the operating conditions present in the aerospace field including the wide temperature span and high-radiation environment. Further, the layout parasitics extraction (LPE) and the smooth transition of CST-derived S-parameters into the HSPICE realm will make sure that behavior of a passive component is not only taken into consideration in the RFIC performance. The obtained results support the feasibility of the offered concept in the aerospace realm, where mission-critical designs have low performance margins, and performance is expected to be exact and reliable. In the near future, it is expected that integrating Al-based layout optimization strategies and radiation-constrained auto-routing tools will also increase the efficiency of the design and robustness of System-in-Package (SiP) realizations of space-based RF front-end modules, leading to the next generation and high-frequency aerospace communication systems.

# **REFERENCES**

- 1. Danh, N. T. (2025). Advanced geotechnical engineering techniques. *Innovative Reviews in Engineering and Science*, 2(1), 22-33. https://doi.org/10.31838/INES/02.01.03

- 2. Castiñeira, M., & Francis, K. (2025). Model-driven design approaches for embedded systems development: A case

- study. SCCTS Journal of Embedded Systems Design and Applications, 2(2), 30-38.

- 3. Kim, J., Lee, H., & Ha, D. (2021). High-fidelity RFIC modeling using HSPICE for mmWave front-end design. IEEE Transactions on Circuits and Systems I: Regular Papers, 68(4), 1050-1062.

- 4. Kavitha, M. (2025). Real-time speech enhancement on edge devices using optimized deep learning models. National Journal of Speech and Audio Processing, 1(1), 1-7.

- Muralidharan, J. (2024). Machine learning techniques for anomaly detection in smart IoT sensor networks. Journal of Wireless Sensor Networks and IoT, 1(1), 15-22. https:// doi.org/10.31838/WSNIOT/01.01.03

- 6. Prasath, C. A. (2025). Adaptive filtering techniques for real-time audio signal enhancement in noisy environments. National Journal of Signal and Image Processing, 1(1), 26-33.

- 7. Singh, A., & Patel, R. (2020). Coupled co-simulation for mmWave RFICs using CST and SPICE tools. Microelectronics Journal, 111, 104949.

- 8. Surendar, A. (2025). Al-driven optimization of power electronics systems for smart grid applications. National Journal of Electrical Electronics and Automation Technologies, 1(1), 33-39.

- 9. Uvarajan, K. P. (2024). Integration of artificial intelligence in electronics: Enhancing smart devices and systems. Progress in Electronics and Communication Engineering, 1(1), 7-12. https://doi.org/10.31838/PECE/01.01.02

- Yaremko, H., Stoliarchuk, L., Huk, L., Zapotichna, M., &Drapaliuk, H. (2024). Transforming economic development through VLSI technology in the era of digitalization. Journal of VLSI Circuits and Systems, 6(2), 65-74. https:// doi.org/10.31838/jvcs/06.02.07

- 11. Zhou, D., Alavi, M. R., &Radhakrishnan, R. (2021). EM simulation of chip-to-package interfaces for Ka-band satellite RF modules using CST. IEEE Transactions on Aerospace and Electronic Systems, 57(3), 1702-1714.