### RESEARCH ARTICLE

# Design and Implementation of Secure VLSI Architectures for Cryptographic Applications

## Dahlan Abdullah

Department of Informatics, Faculty of Engineering, Universitas Malikussaleh, Aceh, Indonesia. Excel engineering college, Komarapalayam, India

### **KEYWORDS:**

Secure VLSI, Cryptographic Applications, Hardware Security, Fault-tolerant Design

### ARTICLE HISTORY:

Submitted: 14.03.2024 Revised: 19.03.2024 Accepted: 22.04.2024

### DOI:

https://doi.org/10.31838/JIVCT/01.01.05

## **A**BSTRACT

The creation and deployment of secure Very-Large-Scale Integration (VLSI) architectures for cryptographic purposes are paramount in safeguarding data and ensuring privacy in today's digital landscape. This article addresses the difficulties encountered in developing secure VLSI systems, including the need to resist physical attacks, meet performance requirements, and maintain power efficiency. We investigate various methods used to bolster the security of VLSI architectures, such as hardware-based protections, advanced encryption techniques, and fault-tolerant designs. The discussion covers implementation strategies, focusing on design methodologies, manufacturing processes, and validation techniques. Through specific case studies, we analyze successful real-world applications of secure VLSI architectures and their effectiveness in protecting sensitive information. Finally, we explore emerging trends and future directions in this field, stressing the necessity for ongoing innovation to combat evolving security threats. This detailed review aims to provide valuable insights for researchers and professionals dedicated to advancing secure VLSI designs for cryptographic applications.

Author's e-mail: dahlan@unimal.ac.id

How to cite this article: Dahlan Abdullah, Design and Implementation of Secure VLSI Architectures for Cryptographic Applications. Journal of Integrated VLSI, Embedded and Computing Technologies, Vol. 1, No. 1, 2024 (pp. 21-25).

## **Introduction**

The growing reliance on digital communication and data exchange has intensified the need for secure data transmission. Cryptographic applications play a crucial role in protecting sensitive information by ensuring its confidentiality, authenticity, and integrity [1]. As

technology advances, embedding cryptographic functions into hardware using Very Large Scale Integration (VLSI) architectures has become essential for achieving high performance and robust security. This strategy allows for the development of specialized hardware optimized for cryptographic tasks [2]. Figure 1 shows the applications of VLSI technology.

Figure 1. Applications of VLSI technology

VLSI technology enables the integration of complex cryptographic algorithms directly onto silicon chips, providing significant advantages over software-based solutions. Hardware implementations of cryptographic algorithms offer enhanced speed and efficiency because they can execute operations in parallel and are optimized for specific tasks [3]. This is particularly important for applications requiring real-time processing, such as secure communications, financial transactions, and military operations. Additionally, hardware-based cryptographic systems are susceptible to certain types of attacks, such as software tampering and side-channel attacks, making them preferred choice for high-security а environments.

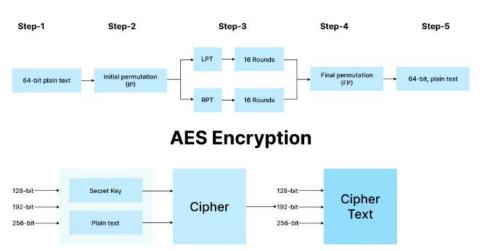

Designing secure VLSI architectures for cryptographic applications involves several critical considerations, beginning with the selection of cryptographic algorithms. The choice of algorithms must balance security, performance, and resource constraints. Common cryptographic algorithms include symmetric key algorithms like Advanced Encryption Standard (AES), asymmetric key algorithms like RSA, and hashing algorithms like SHA-256 [4]. The comparison between AES and RSA encryption is shown in Figure 2. Each of these algorithms has distinct characteristics and requirements that influence the design of the VLSI architecture.

## **DES Encryption**

Figure 2. RSA vs. AES Encryption

Security is the primary concern when designing cryptographic VLSI architectures. Hardware implementations must be resilient against various types of attacks, including side-channel attacks, fault injection attacks, and reverse engineering. Sidechannel attacks exploit information leakage from the implementation cryptographic physical of the algorithm. such as power consumption electromagnetic emissions, to infer secret keys [5]. To counter these attacks, designers use measures such as masking, hiding, and noise generation. Fault injection attacks involve deliberately introducing faults into the hardware to disrupt its normal operation and extract sensitive information. Countermeasures against fault injection attacks include redundancy, error detection and correction codes, and robust design techniques that can tolerate faults without compromising security. The physical design of the VLSI chip is also crucial for ensuring security. This includes layout design, packaging, and testing. The layout must be carefully crafted to minimize signal leakage and cross-talk, which could potentially be exploited by attackers. Packaging techniques such as tamper-evident and

tamper-resistant packaging are used to protect the chip from physical tampering. Additionally, rigorous testing is required to ensure that the chip operates correctly and securely under various conditions. This includes functional testing to verify the correctness of the cryptographic operations and security testing to identify and mitigate potential vulnerabilities.

The rapid evolution of technology and the increasing sophistication of attacks necessitate continuous updates and improvements to cryptographic VLSI architectures. This requires a flexible and adaptable approach that can accommodate algorithms, countermeasures, and security features as they emerge [6]. Reconfigurable hardware, such as Field-Programmable Gate Arrays (FPGAs), offers a promising solution in this regard. FPGAs allow for the dynamic reconfiguration of the hardware, enabling updates and enhancements to be made deployment without the need for physical modifications to the chip. The integration of cryptographic functions into VLSI architectures also opens up new opportunities for innovation and advancement. For instance, the development of quantum-resistant cryptographic algorithms, which can withstand attacks from quantum computers, is an area of active research. Implementing these algorithms in VLSI architectures will be crucial for future-proofing cryptographic systems against emerging threats.

# Challenges in Designing Secure VLSI Architectures for Cryptography

Creating secure VLSI architectures for cryptographic applications comes with several hurdles, mainly centered around safeguarding sensitive data from potential attacks while ensuring efficient performance and reliable functionality. A crucial challenge lies in selecting and implementing cryptographic algorithms that can maintain a balance between security, performance, and resource limitations [7]. These algorithms need to be robust enough to withstand known attacks while also meeting the speed and efficiency requirements of the intended application. Moreover, their hardware implementation must be optimized to make efficient use of resources and minimize power consumption without compromising security.

Another significant obstacle is addressing side-channel attacks, which exploit unintended information leakage from the physical implementation of cryptographic algorithms. These attacks, such as timing or power analysis, can expose sensitive data, like secret keys, by observing the device's physical characteristics during operation. To counter such threats, VLSI architectures must be designed to resist side-channel attacks by considering factors like power usage, electromagnetic emissions, and timing variations. Countermeasures like masking, randomization, and noise injection are commonly used to thwart these attacks and prevent information leakage.

Fault injection attacks present yet another challenge in designing secure VLSI architectures for cryptography. These attacks involve intentionally introducing faults into the hardware to disrupt normal operation and extract sensitive information [8]. Techniques like voltage glitching or laser fault injection compromise cryptographic implementations by causing errors or revealing secret keys. To mitigate such risks, implement countermeasures such designers redundancy, error detection, and fault tolerance to minimize the impact of fault injection attacks and maintain the integrity and confidentiality cryptographic operations.

Physical security is also a significant concern in designing secure VLSI architectures for cryptography, as attackers may attempt physical tampering to gain unauthorized access to sensitive information or manipulate device functionality. To thwart physical attacks, robust packaging techniques, tamper-evident seals, and tamper-resistant enclosures are utilized to prevent unauthorized access to the device [9]. Additionally, features like secure booting, anti-tamper sensors, and intrusion detection mechanisms can detect and respond to physical tampering attempts,

ensuring the integrity and confidentiality of cryptographic operations.

Moreover, ensuring the correctness and reliability of cryptographic VLSI architectures poses a substantial challenge. Designers must rigorously test and verify the hardware implementation of cryptographic algorithms to ensure proper operation under various conditions and resistance to attacks. This involves functional testing to validate cryptographic operations, security testing to identify and address vulnerabilities, and reliability testing to ensure the robustness of the design. Continuous monitoring and updating of cryptographic VLSI architectures are also crucial to adapt to evolving threats and vulnerabilities and maintain long-term security.

## **Techniques for Enhancing Security in VLSI Architectures**

Improving security in VLSI architectures entails deploying a range of techniques to safeguard sensitive data and thwart unauthorized access or manipulation. These methods encompass cryptographic approaches and physical security measures aimed at preserving the confidentiality, integrity, and availability of information handled by VLSI-based systems.

One key tactic for bolstering security in VLSI architectures involves employing cryptographic algorithms to encrypt sensitive data and uphold its confidentiality. Common encryption schemes like AES and RSA are utilized to protect data during storage, transmission, and processing by using keys for encryption and decryption. Additionally, cryptographic hash functions such as SHA are employed to verify data integrity and identify unauthorized alterations.

Effective key management is another vital aspect of enhancing security in VLSI architectures. This entails securely generating, storing, distributing, and disposing of cryptographic keys to prevent unauthorized access or misuse. Dedicated hardware components like HSMs and TPMs are utilized to securely generate and store cryptographic keys, providing protection against key theft or tampering. Key establishment protocols like TLS and Diffie-Hellman key exchange are employed to securely negotiate and exchange encryption keys between parties.

Implementing access control mechanisms is crucial for controlling access to sensitive resources and thwarting unauthorized users from accessing or modifying critical data. Access control models like RBAC and MAC assign permissions and privileges to users based on their roles or security labels, enforcing security policies and limiting access to resources based on predefined rules. Authentication mechanisms such as passwords, biometrics, and multifactor authentication are utilized to authenticate users and ensure secure access to VLSI-based systems.

To counter physical attacks, VLSI architectures integrate various hardware security measures to prevent tampering, reverse engineering, or unauthorized access to sensitive components. These

measures include tamper-resistant packaging, secure booting mechanisms, and anti-tamper sensors that detect and respond to physical intrusion attempts. Additionally, techniques like hardware obfuscation, layout randomization, and logic locking are used to deter reverse engineering and safeguard intellectual property in VLSI designs.

Furthermore, secure communication protocols are employed to guarantee the confidentiality, integrity, and authenticity of data exchanged between VLSI-based systems and external entities. Protocols such as TLS, SSL, and IPsec offer end-to-end encryption and authentication for secure data transmission over networks. These protocols utilize cryptographic techniques like digital signatures and MACs to verify data authenticity and protect against eavesdropping or tampering during communication.

# **Implementation Strategies for Cryptographic VLSI Systems**

Developing cryptographic VLSI systems necessitates meticulous attention to various design elements to security and ensure both efficiency. Multiple implementation strategies are deployed to seamlessly integrate cryptographic algorithms into **VLSI** architectures, addressing concerns related to performance, area overhead, and power consumption while upholding security standards.

A critical aspect of cryptographic VLSI system selecting appropriate implementation involves cryptographic algorithms that strike a harmonious balance between security and efficiency. Algorithms like AES, RSA, and ECC are commonly embraced owing to their established security and widespread adoption. Nonetheless, designers must assess algorithmic performance intricacy, resource requisites, and implications to determine the optimal algorithm for the intended application [10]. Lightweight cryptographic algorithms such as Simon and Speck are preferred for devices with resource constraints, while more computationally demanding algorithms may employed in environments requiring heightened security.

Enhancing cryptographic algorithm implementations for VLSI architectures entails incorporating hardware-accelerated cryptographic primitives to bolster performance and efficiency. Dedicated hardware modules like AES accelerators and RSA co-processors are seamlessly integrated into VLSI designs to alleviate cryptographic computation burdens from the primary processor, thus minimizing processing overhead. These hardware accelerators are fine-tuned for specific cryptographic operations, enabling swifter encryption and decryption processes while curbing energy consumption and area overhead.

Efficient key management strategies are indispensable for securely handling cryptographic keys and safeguarding their confidentiality and integrity. It is imperative to devise robust mechanisms for key storage, generation, distribution, and revocation to

prevent unauthorized access or misuse of cryptographic keys. Hardware security modules (HSMs) and trusted platform modules (TPMs) are widely adopted for securely storing cryptographic keys and executing key management operations, shielding keys against tampering or extraction attempts.

Furthermore, hardware security measures integrated to shield cryptographic VLSI systems from physical attacks and vulnerabilities related to side channels. Countermeasures like side-channel analysis (SCA) countermeasures, secure boot mechanisms, and tamper-resistant packaging are instrumental in mitigating physical attacks and thwarting attempts by adversaries to extract sensitive data or compromise system integrity. Designers resort to layout-level countermeasures such as shielded gates, power gating, and random logic insertion to bolster resistance against side-channel attacks and diminish susceptibility to physical tampering.

## **Case Studies**

In real-world scenarios, the implementation of secure VLSI architectures requires meticulous adherence to cryptographic principles and robust system design methodologies to withstand potential security threats and ensure dependable operation. Various case studies highlight the effective integration of secure VLSI architectures across different domains, demonstrating their effectiveness in protecting sensitive data and facilitating secure communication.

One prominent application area for secure VLSI architectures is in IoT devices, where they play a crucial role in safeguarding the integrity and data exchanged confidentiality of interconnected smart devices. For instance, in smart automation systems, cryptographic implementations are utilized to secure communication channels between devices, gateways, and cloud servers. These architectures often employ lightweight cryptographic algorithms and hardware-accelerated cryptographic modules to enable secure data exchange while minimizing computational overhead and power consumption [11]. Through the integration of robust key management mechanisms and hardware security features, such systems mitigate the risks associated with unauthorized access and data breaches, thereby enhancing user privacy and system security.

Automotive electronics represent another significant domain for secure VLSI architectures, particularly in securing vehicular communication networks and enabling secure access control mechanisms. With modern vehicles incorporating numerous electronic control units (ECUs) interconnected via in-vehicle networks, ensuring robust security is paramount due to potential vulnerabilities associated with wireless communication and networked systems. Secure VLSI architectures are employed to implement cryptographic protocols such as secure key exchange, digital signatures, and message authentication codes to safeguard vehicular communication against potential

threats. By leveraging hardware security modules and embedded cryptographic accelerators, automotive VLSI architectures strengthen vehicle cybersecurity and protect critical systems from malicious attacks and intrusions.

Additionally, secure VLSI architectures find widespread application in financial systems and payment processing platforms, where they are indispensable for ensuring secure transactions and safeguarding sensitive financial information [12]. Payment terminals, ATM machines, and point-of-sale (POS) systems rely on cryptographic VLSI implementations to encrypt transaction data, authenticate users, and securely process payment transactions. These architectures typically utilize hardware security modules and specialized cryptographic processors to execute cryptographic operations efficiently and securely. By adhering to industry-standard encryption algorithms and security protocols, such systems enhance the security of financial transactions, bolster consumer confidence, and foster trust in electronic payment systems.

## **Future Directions and Trends**

Looking forward, the trajectory of secure VLSI cryptographic design is set to tackle upcoming hurdles and leverage technological progress for enhanced security and efficiency. Various future prospects and trends are anticipated to shape the course of secure VLSI cryptographic design, paving the path for innovative solutions and fortified security mechanisms. An important trend involves embedding hardware security features directly into VLSI architectures, aiming to fortify system-wide security and mitigate vulnerabilities. Upcoming VLSI designs are projected to integrate specialized hardware security modules, trusted execution environments, and secure enclaves to furnish hardware-based security functionalities. These components enable secure bootstrapping, cryptographic key management, and protected data processing, bolstering the resilience of cryptographic systems against both physical and logical attacks.

Additionally, the uptake of post-quantum cryptography (PQC) is anticipated to accelerate in response to the looming threat posed by quantum computing to conventional cryptographic algorithms. As quantum computing technologies advance, the imperative for quantum-resistant cryptographic primitives becomes increasingly apparent to safeguard sensitive data against potential decryption threats. Future VLSI cryptographic designs are poised to incorporate PQC algorithms and protocols to ensure sustained security and resilience against quantum adversaries.

Furthermore, advancements in hardware security validation and assurance methodologies are set to propel the development of more dependable and trustworthy VLSI cryptographic implementations. Future designs may capitalize on formal verification techniques, hardware security testing frameworks, and side-channel analysis methodologies to rigorously

confirm the security properties and robustness of cryptographic VLSI architectures. By ensuring adherence to security standards and best practices, these validation techniques augment the reliability and assurance of VLSI cryptographic systems.

Moreover, the proliferation of Internet of Things (IoT) devices and edge computing platforms is poised to influence the design of secure VLSI cryptographic systems, necessitating lightweight and energy-efficient security solutions. Future VLSI designs are expected to prioritize energy efficiency, resource optimization, and scalability to meet the stringent requirements of IoT and edge computing applications. This entails the development of lightweight cryptographic algorithms, hardware-accelerated security modules, and energy-efficient cryptographic protocols tailored for resource-constrained embedded systems.

## REFERENCES

- [1] Christensen, Chris. "Review of cryptography and network security: Principles and practice." Cryptologia 35.1 (2010): 97-99.

- [2] Cohen, Aaron Ethan. Architectures for cryptography accelerators. University of Minnesota, 2007.

- [3] Ancona, Fabio, Alessandro De Gloria, and Rodolfo Zunino. "Parallel VLSI architectures for cryptographic systems." Proceedings Great Lakes Symposium on VLSI. IEEE, 1997.

- [4] Mahajan, Prerna, and Abhishek Sachdeva. "A study of encryption algorithms AES, DES and RSA for security." Global journal of computer science and technology 13.15 (2013): 15-22.

- [5] Randolph, Mark, and William Diehl. "Power side-channel attack analysis: A review of 20 years of study for the layman." Cryptography 4.2 (2020): 15.

- [6] Dhanalakshmi, K. S., and R. Anusha Padmavathi. "A survey on VLSI implementation of AES algorithm with dynamic S-Box." Journal of Applied Security Research 17.2 (2022): 241-256.

- [7] Tehranipoor, Mohammad, and Cliff Wang, eds. Introduction to hardware security and trust. Springer Science & Business Media, 2011.

- [8] Yuce, Bilgiday, Patrick Schaumont, and Marc Witteman. "Fault attacks on secure embedded software: Threats, design, and evaluation." Journal of Hardware and Systems Security 2 (2018): 111-130.

- [9] Vidaković, Marin, and Davor Vinko. "Hardware-Based Methods for Electronic Device Protection against Invasive and Non-Invasive Attacks." Electronics 12.21 (2023): 4507.

- [10] Alsaffar, Dalia Mubarak, et al. "Image encryption based on AES and RSA algorithms." 2020 3rd International Conference on Computer Applications & Information Security (ICCAIS). IEEE, 2020.

- [11] Maitra, Sudip, and Kumar Yelamarthi. "Rapidly deployable IoT architecture with data security: Implementation and experimental evaluation." Sensors 19.11 (2019): 2484.

- [12] Arele, Anshu, and Vikas Sejwar. "A Survey on E-Payment using Quantum and Visual Cryptography." International Journal of Advanced Research in Computer Science 8.5 (2017).