**REVIEW ARTICLE**

# Low-Power Design Techniques for VLSI in IoT Applications: Challenges and Solutions

Dr B.Omkar Lakshmi Jagan

Associate Professor, Department of Electrical and Electronics Engineering, Vignan's Institute of Information Technology (A), Duvada, Visakhapatnam, Andhra Pradesh, India

#### **KEYWORDS:**

Low-power VLSI, IoT applications, Energy efficiency, Dynamic voltage scaling

#### ARTICLE HISTORY:

Submitted:

14.03.2024

Revised:

19.03.2024

Accepted:

22.04.2024

DOI: https://doi.org/10.31838/JIVCT/01.01.01

#### Abstract

Designing low-power Very Large Scale Integration (VLSI) circuits for Internet of Things (IoT) applications presents distinct challenges and significant opportunities. This paper examines the crucial techniques for reducing power consumption in VLSI circuits specifically designed for IoT devices, where energy efficiency is critical. The main methods covered include clock gating, power gating, and dynamic voltage and frequency scaling (DVFS), along with the use of low-power design libraries. The paper also tackles the inherent difficulties in achieving low-power designs, such as balancing trade-offs between power, performance, and area, managing process variations, and ensuring effective thermal management and reliability. By presenting detailed case studies of successful low-power VLSI implementations in IoT devices, the paper highlights practical solutions and best practices. Additionally, it explores future directions and emerging solutions, including the potential of advanced materials, the integration of artificial intelligence for power management, and the development of ultra-low-power and energy-harvesting IoT devices. This comprehensive analysis aims to provide a roadmap for researchers and practitioners in the field, guiding the design of energy-efficient VLSI circuits for the growing IoT ecosystem.

#### Author's e-mail: omkarjagan@yahoo.com

**How to cite this article:** Omkar Lakshmi Jagan B, Low-Power Design Techniques for VLSI in IoT Applications: Challenges and Solutions. Journal of Integrated VLSI, Embedded and Computing Technologies, Vol. 1, No. 1, 2024 (pp. 1-5).

### **INTRODUCTION**

The integration of Very Large Scale Integration (VLSI) technology into Internet of Things (IoT) applications has significantly advanced various sectors, including healthcare, transportation, and smart cities [1]. Figure 1 shows the application of IoT in various fields. As IoT devices become more widespread, the need for low-

power design techniques in VLSI has become more critical [2]. This is driven by the necessity to extend battery life, reduce heat dissipation, and ensure the sustainability of IoT ecosystems, which often operate under strict power constraints. The challenge is to achieve these low-power objectives without compromising performance or functionality.

Figure 1. Applications of Internet of Things (IoT)

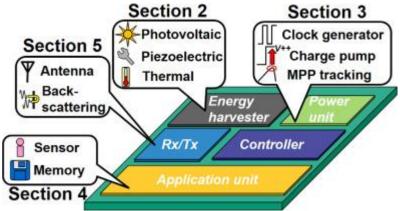

The operational environment of IoT devices primarily drives the need for low-power VLSI design [3]. These devices are often deployed in remote or inaccessible locations where frequent battery replacement or recharging is not feasible [4]. Therefore, extending battery life is of utmost importance. Additionally, IoT devices frequently require continuous operation, gathering and transmitting data in real-time, which exacerbates power consumption issues, making energy efficiency a critical design parameter. The components on standalone LSI chips diverse from the power sources by the energy harvesting, power regulators, application units and data transferring, as shown in Figure 2 [5].

Figure 2. General standalone LSI chip components.

Dynamic voltage and frequency scaling (DVFS) is a highly effective low-power design technique used in VLSI [6]. DVFS adjusts the voltage and frequency according to workload demands, significantly reducing power consumption during low-performance periods. This technique is particularly beneficial for IoT applications, where workload intensity can vary widely depending on the specific task or environmental conditions. By dynamically adjusting power usage, DVFS helps to achieve a balance between performance and energy efficiency.

Power gating is another essential approach, which involves shutting off the power to idle circuits or subsystems within a VLSI chip. By deactivating unused components, power gating minimizes leakage power, which is a significant contributor to total power consumption in modern VLSI designs [7]. For IoT devices, which may spend a considerable amount of time in idle or low-activity states, power gating is an indispensable technique for conserving energy. Similarly, clock gating focuses on disabling the clock signal to inactive circuits, thereby reducing dynamic power consumption by minimizing unnecessary switching activities.

development ultra-low-power The of (ULP) technologies has been crucial in advancing VLSI design for IoT applications. These technologies leverage novel materials, innovative circuit architectures, and advanced manufacturing processes to achieve minimal power consumption. Techniques such as sub-threshold voltage operation, where transistors operate at voltages below their threshold, have shown significant promise. Additionally, energy harvesting, which captures and converts ambient energy sources into electrical power, is gaining traction. Despite these advancements, designing low-power VLSI circuits for IoT applications remains complex, involving trade-offs between power consumption, performance, and area, while ensuring reliability and robustness in varying environmental conditions. As IoT continues to expand, ongoing research and innovation in low-power VLSI design will be essential to meet the evolving demands of this dynamic field.

# Techniques for Reducing Power Consumption in VLSI Circuits

Minimizing power consumption in VLSI (Very Large Scale Integration) circuits is crucial in contemporary electronics, especially given the increasing demand for energy-efficient devices in areas like mobile phones, IoT devices, and embedded systems [8]. Power consumption in VLSI circuits can be divided into dynamic and static power dissipation. Dynamic power dissipation happens due to the charging and discharging of capacitive loads during circuit switching, while static power dissipation is caused by leakage currents when the circuit is in a non-switching state. Various techniques have been devised to effectively tackle both types of power dissipation.

One primary method for reducing dynamic power consumption is Dynamic Voltage and Frequency Scaling (DVFS). DVFS involves dynamically adjusting the voltage and frequency of a processor based on workload requirements. By lowering the voltage and frequency during low computational demand periods, significant power savings can be achieved, as dynamic power consumption is proportional to the square of the supply voltage and linearly related to the frequency. Implementing DVFS requires careful design of power management units and robust algorithms to predict workloads and adjust voltage and frequency without compromising performance. Another essential technique is Clock Gating, which reduces dynamic power by disabling the clock signal to parts of the circuit that are not in use. In digital circuits, the clock signal is a significant source of power consumption as it drives the switching of flipflops and other synchronous elements [9]. By gating the clock signal, unnecessary switching activities are minimized, leading to substantial power savings. Clock gating can be applied at various levels, from coarsegrain gating, which turns off large sections of a circuit, to fine-grain gating, which disables individual flip-flops or smaller circuit blocks.

Power Gating is a method that targets static power consumption by turning off the power supply to idle circuit blocks, thereby reducing leakage currents [10]. Power gating involves using sleep transistors to disconnect the power supply from specific regions of a circuit when they are not in use. This method is particularly effective in modern CMOS technologies, where leakage currents can constitute a significant portion of the total power consumption. Designers must carefully manage the transition between active and sleep states to ensure minimal impact on performance and system reliability.

Multi-Threshold CMOS (MTCMOS) is another technique aimed at reducing static power consumption. In MTCMOS, transistors with different threshold voltages are used within the same circuit [11]. High-threshold voltage transistors are used in non-critical paths to reduce leakage currents, while low-threshold voltage transistors are employed in critical paths to maintain high performance. This dual-threshold approach helps achieve a balance between power efficiency and performance, making it an effective technique for lowpower VLSI design.

# Challenges in Implementing Low-Power VLSI Designs

Developing low-power VLSI (Very Large Scale designs involves tackling Integration) numerous obstacles due to the intricate balance between design requirements, performance expectations, and the imposed limitations by existing semiconductor technologies. These challenges encompass various dimensions, including technical intricacies, economic considerations, and practical hurdles, all of which must be navigated to achieve successful implementations of low-power VLSI designs.

One of the foremost challenges is to ensure that power reduction techniques do not compromise performance. In numerous applications, particularly those involving high-speed computation or real-time processing, maintaining performance levels is critical. While techniques like Dynamic Voltage and Frequency Scaling (DVFS) and power gating are effective for reducing power consumption, they may adversely affect performance if not meticulously managed. Addressing this challenge necessitates the use of sophisticated algorithms and design strategies to dynamically balance power and performance requirements.

significant hurdle is managing leakage Another currents, which become increasingly problematic as transistor sizes decrease in advanced CMOS technologies. Leakage power, also known as static power dissipation, is a significant concern in modern VLSI circuits due to the utilization of smaller transistors with thinner gate oxides, which are more prone to leakage. Although techniques like Multi-Threshold CMOS (MTCMOS) and power gating can mitigate leakage to some extent, they introduce complexity to the design process and require careful planning to prevent potential issues such as increased delav or susceptibility to variability.

Variability in process parameters poses another critical challenge in low-power VLSI design. As manufacturing processes shrink to nanometer scales, variations in transistor characteristics become more pronounced, resulting in inconsistencies in power consumption and performance. Designers must consider these variations during the design phase, often employing robust design practices and statistical methods to ensure that the final product meets its power and performance targets across various manufacturing conditions.

Thermal management presents a crucial challenge in low-power VLSI design. Reducing power consumption is essential not only for energy efficiency but also for managing the heat generated by densely packed circuits. High power density can lead to thermal hotspots, which can degrade performance and reliability or even cause physical damage to the chip. Effective thermal management strategies, such as efficient heat sinks, thermal-aware design techniques, and dynamic thermal management systems, are necessary to mitigate these risks. However, integrating these solutions without significantly increasing the design's complexity or cost is a daunting task.

Integrating low-power techniques into the design flow poses yet another significant challenge. Traditional design flows are optimized for performance and area, and incorporating power reduction techniques often necessitates significant modifications to these established processes. Designers must integrate poweraware design tools and methodologies, which can be complex and time-consuming. Ensuring compatibility between different tools and design stages, from highlevel architectural design to physical implementation, requires comprehensive planning and coordination.

### Case Studies of Low-Power VLSI Designs in IoT Devices

Low-power VLSI designs hold significant importance in IoT devices, where energy efficiency is crucial due to their often remote or battery-operated nature and limited power resources. Several case studies illustrate successful implementations of low-power VLSI designs in IoT devices, showcasing innovative strategies to achieve optimal power consumption while maintaining functionality and performance.

For instance, one notable case study focuses on designing low-power sensor nodes for environmental

monitoring in IoT applications [12]. These nodes are often deployed in harsh or remote environments where power sources are scarce. To tackle this challenge, designers employ various power-saving techniques like duty cycling, where the node alternates between active and sleep modes to conserve energy. They also use ultra-low-power microcontrollers and energyefficient communication protocols to minimize power consumption during data transmission and processing, enabling prolonged operation without frequent battery replacements.

Another compelling example involves developing lowpower wearable devices for health and fitness tracking [13]. These devices demand continuous monitoring of physiological parameters while maintaining a compact form factor and long battery life. To achieve this, designers utilize low-power sensors, efficient signal processing algorithms, and power management techniques. Motion sensors detect user activity and trigger data acquisition only when necessary, while advanced signal processing algorithms enable real-time analysis of sensor data on the device itself, reducing the need for energy-intensive communication with external servers.

In energy harvesting, low-power VLSI designs play a pivotal role in creating self-sustaining IoT devices that derive power from ambient energy sources such as solar or kinetic energy. One case study involves wireless sensor nodes powered by energy harvesting modules. These nodes integrate ultra-low-power microcontrollers and wireless communication protocols to minimize power consumption during operation. Additionally, harvesting modules like energy solar cells or piezoelectric generators capture ambient energy and convert it into electrical power, enabling indefinite operation without external power sources.

Furthermore, low-power VLSI designs are crucial for enabling edge computing and decentralized processing in IoT devices. Edge computing reduces latency, bandwidth usage, and dependency on cloud resources, making it beneficial for real-time or mission-critical IoT applications. Case studies demonstrate how low-power microcontrollers with built-in processing capabilities perform edge computing tasks such as data filtering and inference on-device. By offloading computation from the cloud to the edge, these devices conserve energy and bandwidth while maintaining data privacy and security.

### Future Directions and Emerging Solutions in Low-Power VLSI for IoT

Looking forward, the realm of low-power VLSI for IoT is poised for continuous advancement, propelled by new technologies and evolving application demands. Various future directions and emerging solutions are anticipated to enhance the energy efficiency, functionality, and scalability of VLSI designs for IoT applications.

One notable direction is the incorporation of emerging semiconductor technologies like

nanoelectromechanical systems (NEMS) and spintronics into VLSI designs. NEMS devices offer ultra-low power consumption and high sensitivity, making them wellsuited for sensor nodes and energy-efficient computing. Spintronics leverage electron spin to store and process data, enabling non-volatile memory and low-power logic circuits. By integrating these advanced technologies into VLSI designs, designers can achieve even greater energy efficiency and performance in IoT devices.

Another area of focus is the development of novel architectures and design methodologies optimized for low-power operation in IoT devices. This includes exploring asynchronous and event-driven computing paradigms that eliminate the need for clock signals, reducing dynamic consumption. thus power Additionally, hierarchical and reconfigurable architectures enable dynamic adaptation to changing workloads and environmental conditions, further enhancing energy efficiency and flexibility in IoT systems.

#### REFERENCES

- Barbe, David F., ed. Very large scale integration (VLSI): fundamentals and applications. Vol. 5. Springer Science & Business Media, 2013.

- [2] Bellaouar, Abdellatif, and Mohamed Elmasry. Lowpower digital VLSI design: circuits and systems. Springer Science & Business Media, 2012.

- [3] Gonzalez, Ricardo, Benjamin M. Gordon, and Mark A. Horowitz. "Supply and threshold voltage scaling for low power CMOS." IEEE Journal of Solid-State Circuits 32.8 (1997): 1210-1216.

- [4] Zachariah, Thomas, et al. "The internet of things has a gateway problem." Proceedings of the 16th international workshop on mobile computing systems and applications. 2015.

- [5] Sugiura, Takaya, et al. "Circuits and devices for standalone large-scale integration (LSI) chips and Internet of Things (IoT) applications: A Review." Chip (2023): 100048.

- [6] Garg, Deepak, and Rajender Sharma. "Low power multiplier using dynamic voltage and frequency scaling (dvfs)." 2014 International Conference on Advances in Computing, Communications and Informatics (ICACCI). IEEE, 2014.

- [7] Roy, Kauschick, Saibal Mukhopadhyay, and Hamid Mahmoodi-Meimand. "Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOS circuits." Proceedings of the IEEE 91.2 (2003): 305-327.

- [8] Min-Allah, Nasro, et al. "Towards dynamic voltage scaling in real-time systems-a survey." International Journal of Computer Sciences and Engineering Systems 1.2 (2007): 93-103.

- [9] Shinde, Jitesh, and S. S. Salankar. "Clock gating—A power optimizing technique for VLSI circuits." 2011 annual IEEE India conference. IEEE, 2011.

- [10] Thamaraimanalan, T., and P. Sampath. "Leakage power reduction in deep submicron VLSI circuits using delaybased power gating." National Academy Science Letters 43 (2020): 229-232.

- [11] Bailey, Andrew, et al. "Multi-threshold asynchronous circuit design for ultra-low power." Journal of Low Power Electronics 4.3 (2008): 337-348.

- [12] Nguyen, Cuong M., et al. "Wireless sensor nodes for environmental monitoring in Internet of Things." 2015 IEEE MTT-S International Microwave Symposium. IEEE, 2015.

- [13] Dieffenderfer, James, et al. "Low-power wearable systems for continuous monitoring of environment and health for chronic respiratory disease." IEEE journal of biomedical and health informatics 20.5 (2016): 1251-1264.