Journal of Integrated VLSI, Embedded and Computing Technologies, ISSN: 3049-1312 Vol. 2, No. 1, 2025 (pp. 46-52) RESEARCH ARTICLE ECEJOURNALS.IN

# **Energy Efficient VLSI Design for Next Generation IoT Devices**

#### Fahad Al-Saud<sup>1</sup>, Mohammed Al-Farsi<sup>2\*</sup>

<sup>1,2</sup>Department of Electrical & Computer Engineering Effat University Jeddah, Saudi Arabia

| Keywords:<br>Energy-Efficient VLSI;<br>Low-Power Design;<br>IoT Device Optimization;<br>VLSI Circuit Design;<br>Sustainable Electronics | <b>Abstract</b><br>Mankind has turned into an era where our environment will gradually accept<br>a place to modify how we connect to it, the Internet of Things (IoT). This<br>technological shift is based on the critical requirement of energy efficient<br>Very Large Scale Integration (VLSI) circuits. These are the same circuits as<br>the core of the IoT edge circuits to receive, process, and transmit data in                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Corresponding Author Email:<br>Alfari.mh@effatuniversity.edu.<br>sa<br>DOI: 10.31838/JIVCT/02.01.06                                     | the minimum power consumption. Now that is the demand for low power VLSI solutions in the emerging world of IoT ecosystem. The authors discuss in this article the design intricacies of VLSI circuits intended for the special applications in the IoT. On the way we will discover emerging technologies, new ideas and exciting breakthroughs in the field of energy efficiency. Other strategies to make IoT hardware better: none shall be spared, and we will go from architectural innovations to circuit level optimizations, and beyond. In this comprehensive guide, readers will learn about the challenges in low power VLSI design for IoT, what are these solutions and how IoT future will |

| Received:18.11.2024Revised:20.12.2024Accepted:18.01.2025                                                                                | <ul> <li>power VLSI design for lor, what are these solutions and now for future with look like. Now, if you are a engineer, researcher or a tech enthusiast this article presents some very useful tips on how to start designing energy efficient loT hardware.</li> <li>How to cite this article: Al-Saud F, Al-Farsi M (2025). Energy Efficient VLSI Design for Next Generation IoT Devices. Journal of Integrated VLSI, Embedded and Computing Technologies, Vol. 2, No. 1, 2025, 46-52</li> </ul>                                                                                                                                                                                                    |

### THE IOT REVOLUTION AND THE NEED FOR LOW POWER VSLSI

In the context of the proliferation of IoT devices, industries and daily life have passed through little short of revolution. However, IoT technology is becoming ubiquitous: smart homes, industrial automation and so on. But such rapid expansion comes at a big price: power consumption.<sup>[1]</sup>

#### An Analysis of the Power Predicament in **IoT Devices**

Mostly, the IoT devices work in harsh and diversified ambiances such as where the access of continuous power sources is hindered. The design and functionality of many of these devices rely on batteries or energy harvesting techniques, and hence their power efficiency is the critical factor in the design of the system. In order to enable ultra low power and tight power aware solutions while with very low energy footprint and high battery life of IoT networks, hardware designers have a tremendous pressure.

#### VLSI Circuits: The Unsung Heroes of IoT

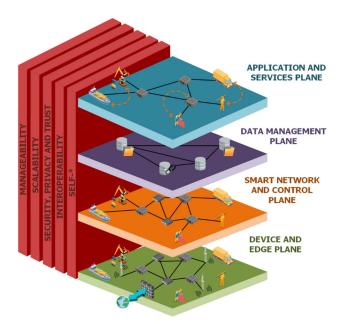

At the heart of every IoT device is, however, VLSI circuits. These integrated circuits handle data processing, communications control, and other various functions of this device. To cater to the increasing need of more sophisticated IoT applications, the circuit with an increasing complexity is required. As the system increases in complexity, power consumption is high, therefore, there is a high design challenge (Figurre 1).

#### **Balancing Power Consummation vs.** Performance

The main challenge of designing VLSI circuits for IoT applications has been that such a balance between performance and power consumptions is difficult to achieve. IoT devices have to become more capable of performing ever more complex tasks at the same time

Fig. 1: Balancing Power Consummation vs. Performance

with less and less energy usage required. The circuit design and optmization have to be innovative for this delicate balance.

# Environmental Impact and Sustainability issues

As more people are coming to realize, there is also a larger issue of environmental impact from building out those IoT deployments. With billions of devices that will be used in the next couple of years, even small gains in energy efficiency translate into massive reductions in total power consumed and electronic waste.

#### Fundamentals of Low Power VLSI Design.

For this reason, understanding the basic principle of low power VLSI design for the IoT application can avoid diving directly into the optimization technique. There are more sophisticated strategies that are built on these principals.<sup>[2-5]</sup>

# **VLSI CIRCUITS POWER DISSIPATION**

In general, there are three main components of power dissipation in VLSI circuits.

- 1. This forms the Dynamic Power Consumption, due to the fact that a capacitive load is being charged and discharged during transistor switching.

- 2. Static Power Consumption: It refers to as the leakage power consumed by the circuit when it is idle.

3. At the switching time, when both PMOS and NMOS are conducting for a brief period, this power consumption occurs.

To develop effective power reduction strategies, these components should be understood.

#### **Power Consumption Eating Key Factors**

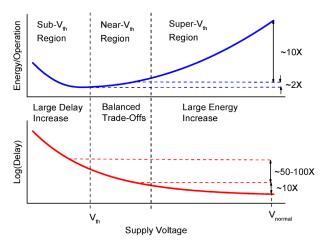

There are several important factors, which influence the power consumption of VLSI circuits. Supply voltage: Since the power consumption grows quadratically with the supply voltage, voltage reduction is a powerful energy efficiency tool all the more. Dynamic power consumption is directly proportional to the switching activity, i.e., the frequency of the transistor state changes. Thus, the power consumption due to charging and discharging of larger size capacitive loads is high. Shrinking transistor sizes make leakage currents an increasing percentage of the overall power consumption. The power efficiency of VLSI circuits is primarily dependent on the ultrahigh precision of manufacture of the semiconductor industry. The processes associated with lower power have smaller processes, and the price is the increase leakage currents.[6-7]

# **P**OWER OPTIMIZATION AND **D**ESIGN **H**IERARCHY

Optimization of power at multiple levels of VLSI design abstraction are as follows:

Range from High level Architectural decisions and Power management Strategies till System Level. It works on Energy efficiency of computational algorithms (Algorithm Level). Circuit Level: Addresses transistor level optimizations and low power circuit techniques. Layout and physical design considerations for power reduction are addressed on the physical level.

The effective low power design at these level requires a holistic approach. Given the desire to make ever more energy efficient IoT devices, researchers and engineers are continuously pushing the boundaries of low power VLSI design. These advanced methods allow a power reduction that was previously considered impossible, but which meet or exceed performance.

#### **Dynamic Voltage and Frequency Scaling** (DVFS)

DVFS enables the processor's voltage and frequency to be dynamically adjusted. Such an adaptive approach allows for optimization of power consumption on a real time basis.

Journal of Integrated VLSI, Embedded and ComputingTechnologies | Jan - April | ISSN: 3049-1312

- 1. The system constantly monitors the amount of computations placed on the processor.

- 2. Performance Assessment is formed based on the monitored workload and the level of the required performance.

- 3. Dynamic voltage and frequency adjustment: Processor voltage and frequency are scaled dynamically in order to match performance requirements with power consumption.

# EMERGING TECHNOLOGIES ULTRA LOW POWER IOT DEVICES

Due to increased demand of energy efficient IoT devices, researchers have started exploring the novel technology for the revolution of low power VLSI design. However, with the current, fast evolving IoT hardware and the increasing deployment of these emerging solutions in real product designs, they can spawn dramatic improvements in energy efficiency and expose the next generation of IoT hardware.<sup>[8-9]</sup>

#### **Beyond-CMOS Technologies**

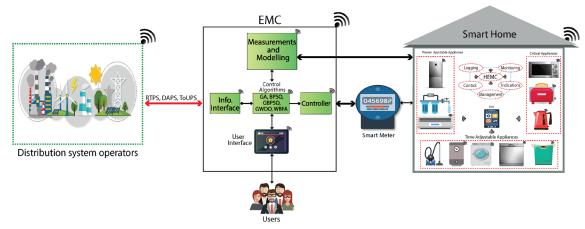

CMOS technology has proved to be a work horse of VSLI design for years while consequently several new materials and device structures have been investigated to get round the limitations of silicon based traditional transistors. For the next generation of IoT applications to fly, ultra low power IoT (Internet of Things) devices are essential as they need to survive on very limited energy sources for prolonged periods remotely in places which are difficult to reach. With the objective to consume very minimal power yet should be functional, these devices can be used across a wide variety of applications including healthcare monitoring, environmental sensing, smart cities, industrial automation, and so on. At the same time, there is always a need for the low power devices, and hence new emerging technologies have developed to make energy efficient solutions for the IoT systems (Table 1).

Advancement of semiconductor materials and fabrication processes is among the key technologies that power ultra-low power IoT devices. New material such as gallium nitride (GaN) and silicon carbide (SiC) have begun to complement the traditional silicon based transistors that are now providing better power efficiency and heat dissipation than the silicon based transistors. By utilizing these materials, switching speeds can be faster and energy consumption can be lower which is particularly crucial for IoT devices which are designed to remain on and operate continuously or for extensive periods of time on minimal power. Energy harvesting is another emerging technology that allows IoT devices to get energy from their surroundings (solar, vibration, thermal, RF, etc.) for enabling long term continuous sensing. Energy harvesting techniques that can reduce or eliminate the need for external power supply or battery can make devices truly autonomous and sustainable. Small scale energy harvesters can be integrated into IoT devices as these can continue working without battery replacement as required in applications such as environmental monitoring or wearable health devices.<sup>[10-11]</sup>

Additionally, ultra-low power communication protocols are an important component of building energy efficient IoT devices themselves. Cost effective but challenging to operate, new communication technologies such as Low Power Wide Area Networks (LPWAN), Bluetooth Low Energy (BLE) and Zigbee allow IoT devices to communicate over long distances or remain connected and consume minimal power. The

| Challenge                                  | Description                                                                                                  | Impact                                                                                      |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Power Consumption in IoT Devices           | Reducing power consumption while<br>maintaining performance is a signifi-<br>cant challenge for IoT devices. | Increased power consumption can re-<br>duce battery life and affect device ef-<br>ficiency. |

| Design Complexity in Low-Power<br>Circuits | Designing low-power circuits requires<br>managing trade-offs between speed,<br>area, and power.              | Complex designs may increase devel-<br>opment time and lead to performance<br>issues.       |

| Integration of Multiple Functionalities    | Integrating various functionalities like<br>sensing, processing, and communica-<br>tion in a single chip.    | Integration complexity can result in in-<br>creased size, power consumption, and<br>cost.   |

| Thermal Management in VLSI Design          | Managing heat dissipation in compact<br>IoT devices to ensure stable operation.                              | Thermal issues can lead to reduced re-<br>liability and damage to components.               |

Table 1: Advancement of semiconductor materials and fabrication processes

energy consumptions in idle and active states have been optimized using these protocols to fit with very long distance communications in cost effective manner, making them suitable for IoT applications. In addition, approaches for power efficient hardware design are being developed to reduce power even further. Dynamic voltage and frequency scaling (DVFS) in which the operating voltage and frequency of the chip are adjusted dependent on the workload, as well as clock gating where the clock signal to portions of the chip are disabled for which are not in use and thus save power.

In short, technological advances in the area of semiconductor materials, energy harvesting methods, low power communication protocols along the way with efficient design of hardware are pushing the boundaries of ultra low power devices on the IoT. Using these innovations a new generation of energy and resource efficient IoT devices can be deployed reliably at the lower power and size budgets needed to

Fig. 2: Tunnel Field-Effect Transistors (TFETs) characteristics

support rapidly expanding demand from both industries and end consumers for sustainable, autonomous systems. As these technologies mature, the number of opportunities for ultra-low power IoT devices will increase, and the applications of these technologies will become even more varied (Figure 2).<sup>[12-17]</sup>

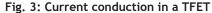

#### **TUNNEL FIELD-EFFECT TRANSISTORS (TFETS)**

Tunnel Field Effect Transistors (TFETs) are becoming significant in high speed and low power electronics as a promising alternative device to traditional MOSFETs (Metal Oxide Semiconductor Field Effect Transistors). The main difference between MOSFETs and TFETs is that TFETs are operated on the quantum tunneling rather than via conventional thermal activation mechanism in MOSFETs. The tunneling phenomenon makes TFETs operate at much lower voltages as compared to conventional FETs, making them highly attractive for power — efficient electronics, specifically for IoT, mobile computing, and low — power logic circuits.<sup>[18-20]</sup>

Current conduction in a TFET is due to quantum mechanical tunneling effect. The application of the gate voltage causes the source channel to be placed in close proximity and the carrier injection resulting from the tunneling instead of the traditional drift mechanism as it exists in MOSFETs. As a result, a much reduced value of the subthreshold swing, a key figure of merit for low power operation, is achieved. Theoretically, TFETs can achieve subthreshold swing below the ideal limit of 60 mV/decade at room temperature, which is lower than MOSFETs of 70-80 mV/decade. The power consumption is very critical in low voltage, low power applications, and this makes TFETs very suitable in such applications (Figure 3).<sup>[21-26]</sup>

Journal of Integrated VLSI, Embedded and ComputingTechnologies | Jan - April | ISSN: 3049-1312

| Solution                                        | Description                                                                                                                               | Benefit                                                                                                     |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Dynamic Voltage and Frequency Scaling<br>(DVFS) | DVFS adjusts the voltage and frequen-<br>cy according to the workload, reducing<br>power consumption during idle times.                   | Helps balance performance and power consumption by adapting to the system, Äôs needs.                       |

| Low-Power CMOS Technology                       | Using low-power CMOS technology al-<br>lows for the reduction of static power<br>consumption in the circuits.                             | Reduces the overall static power con-<br>sumption of IoT devices, extending bat-<br>tery life.              |

| Power Gating and Clock Gating                   | Power gating and clock gating tech-<br>niques selectively turn off idle compo-<br>nents to save energy.                                   | Minimizes energy consumption by se-<br>lectively turning off unnecessary parts<br>of the system.            |

| Energy-Efficient Design Techniques              | Design techniques like multi-threshold<br>CMOS and sub-threshold operation min-<br>imize energy usage while maintaining<br>functionality. | Improves energy efficiency without compromising device performance or speed.                                |

| Advanced Fabrication Processes                  | Advanced fabrication techniques, like<br>FinFET and SOI technologies, provide<br>lower power consumption and higher<br>performance.       | Enhances device performance while<br>ensuring energy savings due to more<br>efficient transistor switching. |

Table 2: MTJ Low read/write energy non volatile memory elements

Particularly, TFETs also offer better performance at lower supply voltage than MOSFETs. As the semiconductor manufacturing process continues to scale transistor sizes, the demand for devices which can function well at low operating voltages is increased. This role is very well suited for TFETs since they continue to drive high current even at reduced gate voltages, which significantly helps to overcome two key problems associated with modern integrated circuits: power consumption and heat dissipation.

However, in practical implementations, they suffer from some issues. The mechanism of tunneling is highly critical with respect to the source and channel materials used, as the goal is to achieve deserving tunneling whilst preserving device performance. Generally, TFETs are fabricated by using more complex material engineering, including using narrow bandgap semiconductor materials such as germanium (Ge) or III - V materials to increase tunneling efficiency. Furthermore, TFETs performance can be impaired, for example due to process variations, which have to be prevented by a careful control during fabrication.<sup>[26-30]</sup>

Generally, TFETs show interesting prospects to improve performance of electronic devices in the sense where power efficiency takes a premium. Although such issues can significantly reduce the prospects for commercial deployment of TFETs within the near future, more research into advances in material properties, fabrication processes and device architectures may soon result in TFETs becoming a common feature of the next generation of ultra-low power electronics and high speed digital circuits.

As a demand for energy-efficient IoT devices keeps on growing, researchers are exploring novel technology that promises to revolutionize low-power VLSI design with its features including MTJ Low read/ write energy non volatile memory elements, Logic in memory architecture and potential in improving the write energy efficiency. Emerging solutions for these problems could provide a significant improvement in energy efficiency as we move towards the next generation of IoT hardware (Table 2).

Thus, a proposal is done of using the neuromorphic computing based on the structure and function of the biological neural network to achieve the energy efficient processing in the IoT devices. As low power consumption for certain types of computation as possible. Successful ability to handle noisy and incomplete data On device learning, and ability to self adapt Efficient neuromorphic hardware architectures to develop Hardware architectures with coherent programming models, tools and languages Integrated with traditional computing paradigms represents the ultimate goal for many IoT applications, which are to create self sustaining devices that may last for ever without external power source.

# CONCLUSION: LOW POWER VLSI DESIGN TO SHAPE THE FUTURE OF IOT

The need for low power VLSI design is becoming an important need, as we are moving towards the edge of a new era of IoT technology. These will be, as you have read in the article above, only the beginning of what will surely become a technological revolution in designing and producing IoT energy efficient devices. Such an insatiable area is fertile for newer, more emerging VLSI low power design space for the IoT space – from circuit level to architectural innovation- and beyond CMOS domain in quantum computing. As researchers and engineers push farther into what's possible, we can expect IoT devices to become more and more energy efficient and capable, as well as more secure, and able to accommodate all sorts of needs for our connected world. But the potential rewards are great, the challenges ahead are large. To enable such IoT technologies to really change every bit of existence, we address the issues of scaling costs, security concerns, and the need for self powered operation. The world will feel the benefits of energy efficient IoT hardware across smart cities, precision agriculture, healthcare, industrial automation, and far beyond. We are looking forward to the future, and we know that future of low power VLSI will keep persisting its effect in future IoT. All of this, we can speed it up by creating collaboration between academia, industry, and open source companies to establish this marketplace and distribute the gain of ultra low power IoT devices to everyone. Across the board in VLSI design, relentless search for energy efficiency is already underway towards truly sustainable, intelligent, and ubiquitous IoT technology.

### **R**EFERENCES:

- Kokolanski, Z., Jordana, J., Gasulla, M., Dimcev, V., & Reverter, F. (2014). Microcontroller-based interface circuit for inductive sensors. Procedia Engineering, 87, 1251-1254.

- Kodali, R. K., Jain, V., Bose, S., & Boppana, L. (2016, April). IoT based smart security and home automation system. In 2016 international conference on computing, communication and automation (ICCCA) (pp. 1286-1289). IEEE.

- Pandey, B., & Pattanaik, M. (2013). Energy Efficient VLSI Design and Implementation on 28nm FPGA: FPGA Based Energy Efficient Register, Memory and ALU Design. LAP LAMBERT Academic Publishing.

- 4. Bello, O., & Zeadally, S. (2014). Intelligent device-to-device communication in the internet of things. IEEE Systems Journal, 10(3), 1172-1182.

- 5. Bello, O., & Zeadally, S. (2014). Intelligent device-to-device communication in the internet of things. IEEE Systems Journal, 10(3), 1172-1182.

- Celdrán, A. H., Clemente, F. J. G., Pérez, M. G., & Pérez, G. M. (2014). SeCoMan: A semantic-aware policy framework for developing privacy-preserving and context-aware smart applications. IEEE Systems Journal, 10(3), 1111-1124.

- Vallabhuni, R. R., Sampath, P., Venkateswarlu, P., Raju, S. S. H., Kumar, M. S., Sonkar, C. K., Srinivas, V., Ramya, V., Dhinakaran, A., Shukla, B. K., Cherian, M. M., & Logeshwaran, J. (2023). *Blockchain-based centralized cloud application in smart cities* (Application No. 202341003902 A). *The Patent Office Journal*, 05/2023, India.

- Van Herrewege, A., Katzenbeisser, S., Maes, R., Peeters, R., Sadeghi, A. R., Verbauwhede, I., & Wachsmann, C. (2012). Reverse fuzzy extractors: Enabling lightweight mutual authentication for PUF-enabled RFIDs. In Financial Cryptography and Data Security: 16th International Conference, FC 2012, Kralendijk, Bonaire, Februray 27-March 2, 2012, Revised Selected Papers 16 (pp. 374-389). Springer Berlin Heidelberg.

- Wallrabenstein, J. R. (2016, August). Practical and secure IoT device authentication using physical unclonable functions. In 2016 IEEE 4th international conference on future internet of things and cloud (FiCloud) (pp. 99-106). IEEE.

- Wortman, P. A., Tehranipoor, F., Karimian, N., & Chandy, J. A. (2017, February). Proposing a modeling framework for minimizing security vulnerabilities in IoT systems in the healthcare domain. In 2017 IEEE EMBS International Conference on Biomedical & Health Informatics (BHI) (pp. 185-188). IEEE.

- 11. Neftci, E. O., Augustine, C., Paul, S., & Detorakis, G. (2017). Event-driven random back-propagation: Enabling neuromorphic deep learning machines. Frontiers in neuroscience, 11, 324.

- 12. Ro, Y., Lee, E., & Ahn, J. H. (2018). Evaluating the impact of optical interconnects on a multi-chip machine-learning architecture. Electronics, 7(8), 130.

- Sarigül, M., & Avci, M. (2018). Performance comparison of different momentum techniques on deep reinforcement learning. Journal of Information and Telecommunication, 2(2), 205-216.

- Roohi, A., & DeMara, R. F. (2019, July). IRC cross-layer design exploration of intermittent robust computation units for IoTs. In 2019 IEEE Computer Society Annual Symposium on VLSI (ISVLSI) (pp. 354-359). IEEE.

- Sirisha, G., Vallabhuni, R. R., Koti, V. M., Goje, N. S., Das, D., Yadav, P., Kumar, K. V., Pradhan, D., Kannan, V., & Logeshwaran, J. (2023). *AI/ML support for ultra-low latency applications at the edge of the network* (Application No. 202341001497 A). *The Patent Office Journal*, 02/2023, India.

Journal of Integrated VLSI, Embedded and ComputingTechnologies | Jan - April | ISSN: 3049-1312

- 16. Shylashree, N., Amulya, M. S., Disha, G. R., Praveena, N., Verma, V. K., Muthumanickam, S., ... & Nath, V. (2023). A novel design of low power & high speed FinFET based binary and ternary SRAM and 4\* 4 SRAM array. IETE Journal of Research, 1-16.

- 17. Yazdanpanah, F. (2023). A low-power wnoc transceiver with a novel energy consumption management scheme for dependable iot systems. Journal of Parallel and Distributed Computing, 172, 144-158.

- Hutter, M., Feldhofer, M., & Wolkerstorfer, J. (2011, June). A cryptographic processor for low-resource devices: Canning ECDSA and AES like sardines. In IFIP International Workshop on Information Security Theory and Practices (pp. 144-159). Berlin, Heidelberg: Springer Berlin Heidelberg.

- 19. Hutter, M., Schilling, J., Schwabe, P., & Wieser, W. (2015, September). NaCl's crypto\_box in hardware. In International Workshop on Cryptographic Hardware and Embedded Systems (pp. 81-101). Berlin, Heidelberg: Springer Berlin Heidelberg.

- Reyhani-Masoleh, A., Taha, M., & Ashmawy, D. (2018, June). New area record for the AES combined S-box/inverse S-box. In 2018 IEEE 25th Symposium on Computer Arithmetic (ARITH) (pp. 145-152). IEEE.

- Shahbazi, K., & Ko, S. B. (2020). High throughput and areaefficient FPGA implementation of AES for high-traffic applications. IET Computers & Digital Techniques, 14(6), 344-352.

- Hamalainen, P., Alho, T., Hannikainen, M., & Hamalainen, T. D. (2006, August). Design and implementation of low-area and low-power AES encryption hardware core. In 9th EUROMICRO conference on digital system design (DSD'06) (pp. 577-583). IEEE.

- 23. Hutter, M., Schilling, J., Schwabe, P., & Wieser, W. (2015, September). NaCl's crypto\_box in hardware. In International Workshop on Cryptographic Hardware and Embedded Systems (pp. 81-101). Berlin, Heidelberg: Springer Berlin Heidelberg.

- 24. Guajardo, J., Güneysu, T., Kumar, S. S., Paar, C., & Pelzl, J. (2006). Efficient hardware implementation of finite fields with applications to cryptography. Acta Applicandae Mathematica, 93, 75-118.

- 25. Balaji, P., Raja, M. S., Kalamani, K., Vallabhuni, R. R., Varghese, J., Suganthi, R., Narayana, S., Ramalashmi, K., Earshia, D. V., Kumar, T. S., Logeshwaran, J., & Kannan, V. (2023). Analysis and detection of depression severity scores based on EEG signal using machine learning approach (Application No. 202341001221 A). The Patent Office Journal, 02/2023, India.

- 26. Hedabou, M., Pinel, P., & Bénéteau, L. (2005). Countermeasures for preventing comb method against SCA attacks. In Information Security Practice and Experience: First International Conference, ISPEC 2005, Singapore, April 11-14, 2005. Proceedings 1 (pp. 85-96). Springer Berlin Heidelberg.

- 27. Ghose, S., Boroumand, A., Kim, J. S., Gómez-Luna, J., & Mutlu, O. (2019). Processing-in-memory: A workload-driven perspective. IBM Journal of Research and Development, 63(6), 3-1.

- Gokhale, M., Holmes, B., & Iobst, K. (1995). Processing in memory: The Terasys massively parallel PIM array. Computer, 28(4), 23-31.

- 29. Wu, Q., & Pan, Z. (2024, May). Performance investigation of doped multi-layer graphene nanoribbon as interconnects in modern technology nodes. In Journal of Physics: Conference Series (Vol. 2757, No. 1, p. 012001). IOP Publishing.

- 30. Bang, K., Chee, S. S., Kim, K., Son, M., Jang, H., Lee, B. H., ... & Ham, M. H. (2018). Effect of ribbon width on electrical transport properties of graphene nanoribbons. Nano convergence, 5, 1-

- Raktur, H., & Jea, T. (2024). Design of compact wideband wearable antenna for health care and internet of things system. National Journal of Antennas and Propagation, 6(1), 40-48.

- 32. Uvarajan, K. P., & Usha, K. (2024). Implement a system for crop selection and yield prediction using random forest algorithm. International Journal of Communication and Computer Technologies, 12(1), 21-26. https://doi. org/10.31838/IJCCTS/12.01.02

- Veerappan, S. (2023). Designing voltage-controlled oscillators for optimal frequency synthesis. National Journal of RF Engineering and Wireless Communication, 1(1), 49-56. https://doi.org/10.31838/RFMW/01.01.06

- 34. Arvinth, N. (2024). Integration of neuromorphic computing in embedded systems: Opportunities and challenges. Journal of Integrated VLSI, Embedded and Computing Technologies, 1(1), 26-30. https://doi.org/10.31838/ JIVCT/01.01.06

- 35. Surendar, A. (2024). Survey and future directions on fault tolerance mechanisms in reconfigurable computing. SCCTS Transactions on Reconfigurable Computing, 1(1), 26-30. https://doi.org/10.31838/RCC/01.01.06

- 36. Abdullah, D. (2024). Recent advancements in nanoengineering for biomedical applications: A comprehensive review. Innovative Reviews in Engineering and Science, 1(1), 1-5. https://doi.org/10.31838/INES/01.01.01

- 37. Kumar, T. M. S. (2024). Low-power communication protocols for IoT-driven wireless sensor networks. Journal of Wireless Sensor Networks and IoT, 1(1), 37-43. https:// doi.org/10.31838/WSNIOT/01.01.06

- 38. Kavitha, M. (2024). Embedded system architectures for autonomous vehicle navigation and control. SCCTS Journal of Embedded Systems Design and Applications, 1(1), 31-36. https://doi.org/10.31838/ESA/01.01.06

- 39. Kavitha, M. (2024). Advances in wireless sensor networks: From theory to practical applications. Progress in Electronics and Communication Engineering, 1(1), 32-37. https://doi.org/10.31838/PECE/01.01.06