# 3D ICs for High-Performance Computing Towards Design and Integration

Tyrell Laa<sup>1</sup>, D.T. Lim<sup>2\*</sup>

<sup>1,2</sup>School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA, USA

# Keywords:

3D Integrated Circuits (3D ICs); High-Performance Computing; IC Design; Vertical Integration; Thermal Management in ICs

Corresponding Author Email: Lim.d41t@ece.gatech.edu

DOI: 10.31838/JIVCT/02.01.01

**Received**: 03.11.2024 **Revised**: 05.12.2024 **Accepted**: 02.01.2025

# **A**BSTRACT

When Industry seeks to drive limits of innovation and continue to meet increasing demands for higher performance, reduced power consumption, smaller form factors in electronic devices. Traditional two dimensional integrated circuit (2D IC) designs are moving towards their physical limit and a new frontier is opened, three dimensional integrated circuits (3D ICs). Such a revolutionary chip design and packaging allows high performance computing to rise above the last stratosphere and usher in a new age of development. In Semiconductor design, 3D ICs are a paradigm shift from conventional planar structure and an alternative to the challenges. 3D ICs achieve extraordinary levels of performance and functionality by stacking active components vertically and interconnecting them using TSVs. A main advantage of this vertical integration is that it leads to shorter interconnects, lower power consumption, and better signal integrity and that is why it is an attractive solution for many tasks in mobiles, data centers and artificial intelligence systems. With this annunciation of a new dimension of chip design, the industry now moves into new challenges and opportunities. To enable the legacy transition to 3D ICs, a radical overhaul of the entire semiconductor ecosystem is required in terms of thermal management and stress analysis, as well as in design tools and manufacturing processes. This article dives deeper into the design and intergration of 3D IC's for high performance computing, and talks about challenges involved in full realization of 3D IC's.

How to cite this article: Tyrell Laa T, Lim DT (2025). 3D ICs for High-Performance Computing Towards Design, and Integration. Journal of Integrated VLSI, Embedded and Computing Technologies, Vol. 2, No. 1, 2025, 1-7

# THE PROMISE OF 3D ICS

3D ICs are a significant step forward in semiconductor technology beyond the limitations of planar based designs with their associated advantages, particularly for high performance computing applications.<sup>[1-2]</sup>

#### **Better Performance and Bandwidth**

However, the increase in the performance and bandwidths is the main benefit of 3D ICs. Stacking along the vertical direction makes it possible to have very short interconnects between different functional units. On the contrary, this decrease in the interconnect length also implies shorter signal propagation delays between elements, which is important because it allows to transfer and process

data faster. The increase in bandwidth can lead to very significant performance boosts to overall system performance for high performance computing systems with heavy data throughput requirements, such as scientific simulations or artificial intelligence applications (Figure 1).<sup>[3-4]</sup>

Fig. 1: 3D ICs

# **Reduced Power Consumption**

Specifically in modern computing systems (data centers, phones etc.) power efficiency is a critical challenge, and 3D ICs allow to reduce the distance for the signals to travel. Short interconnects lead to a lower capacitance and resistance resulting in lowered power consumption. They additionally suggest that redundant heterogeneous components optimized for particular function roles might be less difficult to mix into bigger system designs, hence bettering the power utilization. For instance, a direct stack of memory layers stacked on top of the processing units, directly reduces the energy for data movement and also improves the overall system efficiency. [5-6]

# **Increased Functionality in Smaller Footprint**

3D ICs can achieve an order of magnitude increase of functionality per unit area through vertical integration of components. In particular, it is particularly useful in cases where space is at a premium, i.e. not only on devices (such as mobiles), but also high performance computing systems with limited size. Since chip size is lateral for a die, designers can put more features and functionality on chip with multiple dies on chip. More powerful and variegated computing systems in smaller form factors can be enabled by advances in density of functionality.<sup>[7-9]</sup>

#### SIGNAL INTEGRITY AND TIMING

To exploit the performance benefits of 3D integration, signal integrity must be preserved and timing managed between multiple stacked dies. TSVs for vertical propagation of signal. Electromagnetic interference and inter layer crosstalkin 3D structures, Clock distribution and skew management will be addressed. Cross die timing closure over multiple dies with possibly differentiated process technologiesmultiple stacked dies is crucial for achieving the performance benefits of 3D integration. Designers must account for:

- Vertical signal propagation through TSVs

- Inter-layer crosstalk and electromagnetic interference

- Clock distribution and skew management in 3D structures

- Timing closure across multiple dies with potentially different process technologies

#### **Integration Techniques for 3D ICs**

Successful 3D IC implementation depends on advanced integration techniques to stack and interconnect

multiple dies. However, these techniques have been adapted to circumvent the distinctive challenges of vertical integration and to harness the advantages of 3D architecture.[10-11]

There are several approaches to stacking dies in 3D ICs, each with its own advantages and considerations:

- Face-to-Face Bonding: In this technique, two dies bonded that 'active' sides are facing. However, this approach allows for high density interconnects between the two dies but only to two layer stacks.

- Face-to-Back Bonding: By bonding the face of a first die to the back of a second die, this technique allows the stacking of multiple dies. Vertical connections require TSVs, but a more flexible multi layer stack is allowed.

- Monolithic 3D Integration: This growing technique is to grow a number of layers of dynamic devices on the same wafer. Given its challenges to implement, it promises extremely high density integration.

### **Bonding Technologies**

Interconnections between stacked dies in current system-on-package (SoP) concepts are fundamentally dependent on selected bonding technology.

**Microbump Bonding:** It provides good electrical and mechanical properties using these small solder bumps to connect stacked dies.

**Copper-to-Copper Direct Bonding:** It offers high density interconnects with low resistance at the cost of requiring precise alignment and surface preparation.

**Hybrid Bonding:** It offers high density, low resistance metal-to metal and dielectric to dielectric bonding. [10-14]

# INTERPOSER TECHNOLOGIES

The design of 3D IC systems incorporates interposers as both first and intermediate layers which connect stacked dies to the package substrate. Key interposer technologies include:

The manufacturing expenses of silicon interposers remain challenging due to their high density routing capabilities and their capacity to contain active components.

Device producers can develop glass interposers through panel manufacturing in large quantities which lowers their production price. Provide a lower interconnect density than silicon or glass, at a lower cost but less demanding application (Figure 2). [15-18]

Fig. 2: Interposer Technologies

Table 1: 3D ICs for High-Performance Computing

| Technology                         | Role in 3D IC Design                                                                                                                      | Application in High-Performance<br>Computing                                                              |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Through-Silicon Vias (TSVs)        | TSVs enable vertical electrical connections between different layers of the IC, facilitating multi-layer integration.                     | Facilitates efficient vertical integration for faster data processing and reduced latency.                |

| Wafer-Level Packaging (WLP)        | WLP provides a compact and cost-effective packaging method, improving yield and performance in 3D ICs.                                    | Improves system performance and reduces package size, crucial for high-density computing systems.         |

| Microbumps and Stacking Techniques | Microbumps and stacking techniques enable precise alignment and interconnection between stacked die, ensuring optimal performance.        | Enhances electrical performance in stacked ICs and improves reliability for multi-layer circuits.         |

| Thermal Management Solutions       | Thermal management solutions such as heat spreaders and microfluidic cooling techniques are crucial to manage heat dissipation in 3D ICs. | Ensures stable operation of high-per-<br>formance computing systems by man-<br>aging thermal constraints. |

| Interposer Integration             | Interposer integration allows for heterogeneous integration of components, enhancing functionality and reducing interconnect delays.      | Reduces signal delay and improves data bandwidth, essential for high-performance computing applications.  |

#### **Packaging Considerations**

Packaging of 3D IC shows unique problems and advantages. The needs of 3D integrated systems are met through current development models of advanced packaging technologies that combine fanout wafer-level packaging (FOWLP) and embedded die technologies. The performance benefits of 3D integration depend on three packaging design features including strong electrical connectivity between system board and die thickness and size definition. Designers must account for:

- Vertical signal propagation through TSVs

- Inter-layer crosstalk and electromagnetic interference

Clock distribution and skew management in 3D structures

Multiple die timing closure serves as a critical requirement when working with dies that operate from different process technology platforms (Table 1).[19-20]

# **Integration Techniques for 3D ICs**

Multiple dies can be stacked and interconnected using advanced methods to achieve successful deployments of 3D ICs. The approach to stacking and interconnecting multiple dies has developed specific solutions to manage vertical integration requirements while fully realizing 3D architectural advantages.

# **DIE STACKING METHODS**

Several methods of stacking dies in 3D ICs have been developed, and each offers its own advantages and disadvantages.

- Face-To-Face Bonding: In this, the two dies are bonded with active face to active face. However, it has the advantage of providing high density interconnects between the two dies, but only in two layer stacks.

- 2. Face to back Bonding: This involves bonding of one dies face to another dies back thus allowing one to stack multiple dies in one dimmension. Multichip packaging requires TSVs (i.e. for vertical connections), but provides more flexibility on multi-layer stacks.

- 3. Monolithic 3D Integration is this new approach where multiple layers of active devices are built on a single wafer. Although difficult to implement, huge degrees in area integration are possible.

Selection of the bonding technology is crucial to the formation of reliable interconnections between stacked dies. Common bonding techniques include:

Microbump Bonding: Small solder bumps are used to connect stacked dies and provides good electrical and mechanical properties.

**Copper-to-Copper Direct Bonding:** a low resistance interconnect with high density that is achieved thermocompression bonding copper with high precision and requires careful preparation of the copper surfaces.

**Hybrid Bonding:** Combines metal-to-metal and dielectric-to-dielectric bonding for high-density, low-resistance connections. [21-23]

#### **Interposer Technologies**

Interposers are also used in many 3D IC designs to serve as the intermediate layer that enables connections between the stacked dies and the package substrate. Key interposer technologies include:

High density Routing: Always provides high density routing capability; it can also incorporate active components and offer some mixed signal routing but is costly to manufacture.

Glass Interposers offer good electrical isolation, and can be made large panel sizes which could lower costs. Organic Interposers: For less demanding applications offer cost effective solution with lower interconnect density than silicon or glass.

# **Packaging Considerations**

The issues involved in packaging 3D ICs are unique. To meet the particular requirements of 3D integrated systems, various advanced packaging technologies, including fanout wafer level packaging (FOWLP) and embedded die technologies, are also being developed. These packaging solutions must provide:

- Efficient heat dissipation

- Robust electrical connections to the system board

- Protection from environmental factors

- Allows for the incorporation of die of various thicknesses and sizes in the stack

# 3D IC Design and Integration Challenges

Although it has huge potentials, many design and integration problems exist in 3D ICs for realizing its potentials in high performance computing applications. [24]

# **Thermal Management**

One of the most outstanding issues in 3D IC design is its heat dissipation. In the presence of several active layers stacked, power density increases and so do hotspot creation in the structure. Left untreated, this will result in degraded device performance, reliability problems, and ultimately failure of the device. Integrated heat spreaders or microfluidic channels for advanced cooling

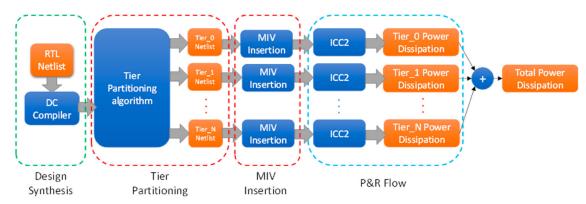

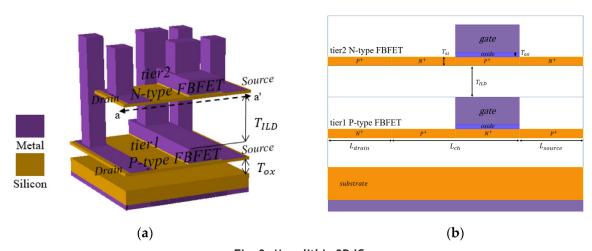

### **Post-Bond Testing**

The problem however is that after dies are stacked and bonded, testing internal layers becomes very difficult to access. Testing strategies after bond must deal with the fact that the interconnections and functioning across the 3D stack have to be verified. Testing in layer to layer fashion and, implementation of 3D scan chains to increase the test access coverage area of the 3DIC test. The testing of 3D architectures becomes challenging for the development of boundary scan techniques. Verification of interconnections and functionality across the 3D stack must be possible according to the post bond testing strategies (Figure 3).<sup>[25-28]</sup>

# Future Directions and Emerging Technologies

There is much rapid pace on emerging new technologies and approaches in the field of 3D ICs for high performance computing. Areas of development which are most promising include:

Fig. 3: Monolithic 3D IC

Table 2: Advanced Integration Techniques

| Integration Technique              | Focus Area                                                                                                                   | Application in High-Performance<br>Computing                                                                                     |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Chip-to-Chip Integration           | Stacking multiple chips vertically to increase density and improve performance in computing systems.                         | Enhances system throughput and memory bandwidth by enabling chip-to-chip communication within a 3D stack.                        |

| Heterogeneous Integration          | Combining different types of chips or technologies (e.g., memory, logic) to optimize performance and functionality.          | Enables the integration of specialized components, optimizing HPC systems for specific tasks.                                    |

| Monolithic Integration             | Integrating different functions (e.g., processor and memory) onto a single die for compactness and performance.              | Increases computational power and reduces footprint in systems requiring compact high-performance solutions.                     |

| Co-Design of Hardware and Software | Simultaneously designing both hard-<br>ware and software to maximize the<br>performance of the integrated system.            | Improves system-level performance by optimizing resource allocation and minimizing delays in data processing.                    |

| System-on-Package (SoP)            | Combining multiple ICs into a single package to enhance functionality, reduce interconnects, and improve system performance. | Enables the packaging of diverse functionalities in a single compact unit, reducing system complexity and improving performance. |

# **Monolithic 3D Integration**

Current 3D IC technologies are based on the process of stacking together separately fabricated dies; while monolithic 3D integration involves assembling active devices by integrating many layers into a single wafer. However, this approach is limited by manufacturing challenges to the highest integration and performance levels with this process.

#### **Optical Interconnects**

Optical interconnects within 3D IC structures enable chip to chip communication with orders of magnitude more bandwidth than interconnects using electrical interconnects, and consume energy efficiency by more than two orders of magnitude better than electrical interconnects. Research is being carried out on practical solutions for integrating 3D architectural photonic components with electronic circuits (Table 2).

# **Advanced Cooling Solutions**

In pursuit of addressing thermal challenges pertaining to high performance 3D ICs, novel cooling technologies like integrated microfluidic channels and phase change materials are being studied. Even more, they may enable for operating of higher levels of integration and performance.

# **Neuromorphics Computing Architectures**

An exciting area in the research is to develop 3D integration of neuromorphic computing elements which are structurally and functionally mimicking the biological neural networks. Such architectures could allow for creating highly efficient, scalable AI systems by virtue of vertical dimension.

### **Quantum Computing Integration**

As quantum computing technology advances, the integration of quantum processing elements with classical control circuitry in 3D structures is taking place. Presented here is the hybrid approach which one day may make quantum computing systems more practical and scalable.

### **C**onclusion

3D ICs are a transformative technology how achieves high performance with dramatic improvements in power efficiency and functionality. With Moore's Law continuously advancing the capabilities of the semiconductor space and computing hardware, 3D integration is the way for the semiconductor industry to keep that pace of advancement in computational capability. Nevertheless, realizing the full potential of 3D ICs comes with several design, manufacturing and test challenges. Meanwhile, efforts in research and development are needed to overcome thermal management problems, increase yield and reliability, and develop the design tools and associated methodologies. Monolithic 3D integration and optical interconnects are emerging technologies with potential of even better performance and efficiency that have been proven to be attractive in general 3D ICs for HPC. Similar to any mature technology, the ecosystem around 3D IC design and manufacturing will mature on the go and it will ultimately open up computing systems that will increasingly use power of the third dimension as the technology continues to mature bit by bit. However, the possibilities of computational power, efficiency in energy use and new application possibilities make the journey towards fully enabling 3D ICs process still ongoing, but an important focus area for the semiconductor industry. Therefore, as the future of researchers, engineers, and manufacturers spend more time innovating and collaborating, 3D IC remain integral in defining the future of high performance computing and creating the next generation of technologies.

#### REFERENCES:

- Gouker, P. M., Tyrrell, B., D'Onofrio, R., Wyatt, P., Soares, T., Hu, W., et al. (2011). Radiation effects in 3D integrated SOI SRAM circuits. IEEE Transactions on Nuclear Science, 58(6), 2845-2854. https://doi.org/10.1109/ TNS.2011.2174998

- 2. Kirschman, R. (1990). Low-temperature electronics. IEEE Circuits and Devices Magazine, 6(3), 12-24. https://doi.org/10.1109/101.54862

- Matick, R. E., & Schuster, S. E. (2005). Logic-based eDRAM: Origins and rationale for use. IBM Journal of Research and Development, 49(1), 145-165. https://doi. org/10.1147/rd.491.0145

- Kleiner, M. B., et al. (1996). Performance improvement of the memory hierarchy of RISC-systems by application of 3-D technology. IEEE Transactions on Components, Packaging, and Manufacturing Technology, Part B: Advanced Packaging, 19(4), 709-718. https://doi. org/10.1109/96.546839

- Kawamura, S., Sasaki, N., Iwai, T., Nakano, M., & Takagi, M. (1983). Three-dimensional CMOS ICs fabricated by using beal recrystallization. IEEE Electron Device Letters, 4(10), 366-368. https://doi.org/10.1109/ EDL.1983.25844

- Kunio, T., Oyama, K., Hayashi, Y., & Morimoto, M. (1989). Three-dimensional ICs, having four stacked active device layers. IEDM Technical Digest, 837-840.

- 7. Vallabhuni, V., et al. (2022). Implementation of fundamental modules using quantum dot cellular automata. Journal of VLSI Circuits and Systems, 4(1), 12-19.

- Subramanian, V., Toita, M., Ibrahim, N. R., Souri, S. J., & Saraswat, K. C. (1999). Low-leakage germanium-seeded laterally-crystallized single-grain 100-nm TFTs for vertical integration applications. IEEE Electron Device Letters, 20(7), 341-343. https://doi.org/10.1109/55.775316

- Sun, J., Lu, J., Giuliano, D., Chow, T. P., & Gutmann, R. J. (2007). 3D power delivery for microprocessors and high-performance ASICs. Proceedings of IEEE Applied Power Electronics Conference, 127-133. https://doi. org/10.1109/APEC.2007.357679

- 10. Tu, Y. L., Lin, H. L., Chao, L. L., Wu, D., Tsai, C. S., Wang, C., Huang, C. F., Lin, C. H., & Sun, J. (2003). Characterization and comparison of high-k metal-insulator-metal (MiM) capacitors in 0.13µm cu BEOL for mixed-mode and RF applications. Proceedings of the IEEE International Symposium on VLSI Circuits, 79-80. https://doi.org/10.1109/VLSIC.2003.1220794

- Waizman, A. (2003). CPU power supply impedance profile measurement using FFT and clock gating. Proceedings of the IEEE Electrical Performance of Electronic Packaging Meeting, 29-32. https://doi.org/10.1109/ EPEP.2003.1249067

- 12. Chen, K. N., Fan, A., Tan, C. S., & Reif, R. (2004). Contact resistance measurement of bonded copper interconnects

- for three-dimensional integration technology. IEEE Electron Device Letters, 51(2), 20-22. https://doi.org/10.1109/LED.2004.832345

- 13. Tan, C. S., Fan, A., Chen, K. N., & Reif, R. (2003). Low-temperature thermal oxide to plasma-enhanced chemical vapor deposition oxide wafer bonding for thin-film transfer application. Applied Physics Letters, 82(16), 2649-2651. https://doi.org/10.1063/1. 1564886

- 14. Selvakanmani, S., et al. (2021). A novel global secure management system with smart card for IoT and cloud computing. The Patent Office Journal No. 06/2021, India.

- 15. Das, S., Chandrakasan, A., & Reif, R. (2003). Design tools for 3-D integrated circuits. Proceedings of ASP-DAC, 53-56.

- 16. Andry, P. S., Tsang, C. K., Webb, B. C., Sprogis, E. J., Wright, S. L., Bang, B., & Manzer, D. G. (2008). Fabrication and characterization of robust through-silicon vias for silicon-carrier applications. IBM Journal of Research and Development, 52(6), 571-581. https://doi.org/10.1147/rd.526.0571

- 17. Lau, J. H. (n.d.). Reliability of RoHS Compliant 2D & 3D IC Interconnects. McGraw-Hill.

- Park, D., et al. (2008). MIRA: A multi-layered on-chip interconnect router architecture. Proceedings of the 35th International Symposium on Computer Architecture (ISCA 08), 251-261.

- 19. Lewis, D. L., & Lee, H.-H. S. (2007). A scan-island based design enabling pre-bond testability in die-stacked microprocessors. Proceedings of the International Test Conference, 1-8.

- 20. Batude, P., et al. (2015). 3DVLSI with CoolCube process: An alternative path to scaling. VLSI Technology (VLSIT), T48-T49.

- 21. Tamboli, M. S., et al. (2023). Blockchain-based integrated data aggregation and segmentation framework by reputation metrics for mobile ad hoc networks. Measurement: Sensors, 27, 100803. https://doi.org/10.1016/j.measen.2023.100803

- 22. Sekar, D. C., & Or-Bach, Z. (2012). Monolithic 3D-ICs with single crystal silicon layers. Proceedings of the 3DIC Conference, 1-2.

- 23. Rajendran, B., et al. (2013). Pulsed laser annealing: A scalable and practical technology for monolithic 3D IC. Proceedings of the 3DIC Conference, 1-5.

- Heya, A., Masuda, A., & Matsumura, H. (1999). Low-temperature crystallization of amorphous silicon using atomic hydrogen generated by catalytic reaction on heated tungsten. Applied Physics Letters, 74(15), 2143–2145. https://doi. org/10.1063/1.123836

- Watts, R. K., & Lee, J. T. C. (1993). Tenth-micron polysilicon thin-film transistors. IEEE Electron Device Letters, 14(11), 515–517. https://doi.org/10.1109/55.260810

- Rodder, M., & Aur, S. (1991). Utilization of plasma hydrogenation in stacked SRAMs with poly-Si PMOSFETs and bulk Si NMOSFETs. IEEE Electron Device Letters, 12(5), 233–235. https://doi.org/10.1109/55.76778

- Vanna-Iampikul, P., Shao, C., Lu, Y.-C., Pentapati, S., & Lim, S. K. (2021). Snap-3D: A constrained placement-driven physical design methodology for face-to-face bonded 3D ICs. Proceedings of the 2021 International Symposium on Physical Design, 39–46.

- 28. Wang, S.-J., Lin, C.-H., & Li, K. S.-M. (2013). Synthesis of 3D clock tree with pre-bond testability. Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), 2654–2657.

- 29. Muralidharan, J. (2024). Advancements in 5G technology: Challenges and opportunities in communication networks. *Progress in Electronics and Communication Engineering*, 1(1), 1–6. https://doi.org/10.31838/PECE/01.01.01

- 30. Muralidharan, J. (2024). Optimization techniques for energy-efficient RF power amplifiers in wireless communication systems. SCCTS Journal of Embedded Systems Design and Applications, 1(1), 1-6. https://doi.org/10.31838/ESA/01.01.01

- Prasath, C. A. (2024). Energy-efficient routing protocols for IoT-enabled wireless sensor networks. *Journal of Wireless Sen*sor Networks and IoT, 1(1), 1-7. https://doi.org/10.31838/WS-NIOT/01.01.01

- 32. Sulyukova, L. (2025). Latest innovations in composite material technology. *Innovative Reviews in Engineering and Science*, 2(2), 1-8. https://doi.org/10.31838/INES/02.02.01

- 33. Sathish Kumar, T. M. (2024). Developing FPGA-based accelerators for deep learning in reconfigurable computing systems. *SCCTS Transactions on Reconfigurable Computing, 1*(1), 1-5. https://doi.org/10.31838/RCC/01.01.01

- 34. Jagan, B. O. L. (2024). Low-power design techniques for VLSI in IoT applications: Challenges and solutions. *Journal of Integrated VLSI, Embedded and Computing Technologies, 1*(1), 1-5. https://doi.org/10.31838/JIVCT/01.01.01

- 35. Muralidharan, J. (2023). Innovative RF design for high-efficiency wireless power amplifiers. *National Journal of RF Engineering and Wireless Communication*, 1(1), 1-9. https://doi.org/10.31838/RFMW/01.01.01

- 36. Yang, C. S., Lu, H., & Qian, S. F. (2024). Fine tuning SSP algorithms for MIMO antenna systems for higher throughputs and lesser interferences. *International Journal of Communication and Computer Technologies*, *12*(2), 1-10. https://doi.org/10.31838/IJCCTS/12.02.01

- 37. Rimada, Y., Mrinh, K.L., & Chuonghan. (2024). Unveiling the printed monopole antenna: Versatile solutions for modern wireless communication. *National Journal of Antennas and Propagation*, 6(1), 1–5.